I want to compliment ChipGuy on a very nice write-up of a complex topic – how to model process variation in static timing.

… Read More

Tag: clkda

In Low Voltage Timing, the Center Cannot Hold

When I started discussing this topic with Isadore Katz, I was struggling to find a simple way to explain what he was telling me – that delay and variance calculations in STA tools are wrong at low voltage because the average (the center) of a timing distribution shifts from where you think it is going to be. He told me that I’m not alone… Read More

The Revenge of Microprocessor Design: The Return of the Macro

(Two Star Wars™ allusions in one title – eat your heart out George Lucas.) Most of us are comfortable with the idea that you design more or less whatever you want in RTL and let the synthesis tool pick logic gates to implement that functionality. Sure it may need a little guidance here and there but otherwise synthesis is more or less … Read More

Ultra-low Voltage: Is Your Slack Really Positive? Are You Sure?

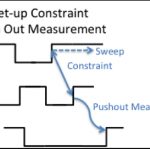

During synthesis and static timing the main figure of merit is “slack”. If a signal arrives with time to spare before it is needed (often measured against the setup time before a clock changes at a register) then the slack is positive. Positive slack is generally a good thing, although it can indicate over-design if … Read More

FinFET: The Miller’s Tale

In Chaucer’s Canterbury Tales, the second of the tales told by the pilgrims is The Miller’s Tale. Since this is a family blog, I’ll leave you to research the tale yourself. But FinFETs hide another Miller’s Tale, due to Miller capacitance, sometimes called the Miller effect. This is significant since in FinFET designs Miller capacitance… Read More

Variation Alphabet Soup

On-chip variation (OCV) is a major issue in timing signoff, especially at low voltages or in 20/16/14nm processes. For example, the graph below shows a 20nm inverter. At 0.6V the inverter has a delay of 2 (nominalized) units. But due to on-chip variation this might be as low as 1.5 units or as high as 3 units, which is a difference from… Read More

Voltage Limbo Dancing: How Low Can You Go?

All chips these days have to worry about power. Indeed it is typically the top of the priority list of concerns, above performance and even area. Transistors are effectively fast and free, but you can’t have too many of them (at least turned on at once). The most obvious way to reduce power is to lower the supply voltage. This … Read More

A Brief History of CLKDA: Every Picosecond Counts Below 28nm

One thing to point out is that the CLK of CLKDA are the initials of the founders, they are not focused on clocks! I’m sure you can guess what DA stands for, although it is also the last two letters of the fourth founder’s name.

They have been in existence since 2005, backed by Atlas Ventures and Morgenthaler. They are headquartered… Read More