You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

In this episode of the Semiconductor Insiders video series, Dan is joined by Chouki Aktouf, CEO and Founder of Defacto Technologies. Dan explores the challenges of building complex SoCs with Chouki, who describes challenges around managing complexity at the front end of the process while staying within PPA requirements and … Read More

Chouki Aktouf is Founder & CEO of Defacto Technologies and Co-Founder of Innova Advanced Technologies. Prior to founding Defacto in 2003, Dr. Aktouf was an associate professor of Computer Science at the University of Grenoble – France and leader of a dependability research group. He holds a PhD in Electric Engineering from… Read More

At #61DAC I stopped by the Defacto Technologies exhibit and talked with Chouki Aktouf, President and CEO, to find out what’s new in 2024. ARM and Defacto have a joint SoC design flow by using the Arm IP Explorer tool along with Defacto’s SoC compiler, which helps to quickly create your top-level RTL, IP-XACT and UPF files. This tool… Read More

When I was at DAC last month, I had the chance to talk with Chouki Aktouf and Bastien Gratréaux from Defacto and they told me about a new innovative solution to generate Arm-based System-on-Chips. I heard that this solution has now been released.

Defacto and Arm developed a joint SoC design flow to help Arm users cover all needed automation—from… Read More

Dan is joined by Chouki Aktouf, founder & CEO of Defacto Technologies and co-founder of Innova Advanced Technologies. Prior to founding Defacto in 2003, Dr. Aktouf was an associate professor of Computer Science at the University of Grenoble – France and leader of a dependability research group. He holds a PhD in Electric Engineering… Read More

I’ve talked with Defacto on and off for several years – Chouki Aktouf (CEO) and Bastien Gratreaux (Marketing). I was in a similar line of business back in Atrenta. Now I’m just enjoying myself, I’ve written a few blogs for them. I’ll confess I wondered why they wouldn’t struggle with the same problems we’d had. Script-driven RTL editing,… Read More

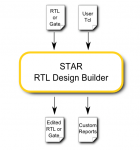

DeFacto and their STAR technology are already quite well known among those who want to procedurally apply edits to system-level RTL. I’m not talking here about the kind of edits you would make with your standard edit tools. Rather these are the more convoluted sort of changes you might attempt with Perl (or perhaps Python these days).… Read More

For the devices we build today, design and implementation are unavoidably entangled. Design for low-power, test, reuse and optimized layout are no longer possible without taking implementation factors into account in design, and vice-versa. But design teams can’t afford to iterate indefinitely between these phases, so they… Read More

It is self-evident that large systems of any type would not be possible without hierarchical design. Decomposing a large system objective into subsystems, and subsystems of subsystems, has multiple benefits. Smaller subsystems can be more easily understood and better tested when built, robust 3[SUP]rd[/SUP] party alternatives… Read More

As a 30+ year semiconductor veteran I can tell you with 100% certainty that start-ups are the lifeblood of EDA. The mantra is “Innovate or Die!” and that is exactly what Defacto is doing. After more than 10 years of innovating in Design for Test at RTL, Defacto is now offering a complete EDA solution based on generic EDA… Read More