In the rapidly evolving landscape of semiconductor manufacturing, the demand for processors that handle increasing workloads while maintaining power efficiency and compact form factors has never been higher. Intel’s Foveros 2.5D packaging technology emerges as a pivotal innovation, enabling denser die integration… Read More

Tag: chiplet

eBook on Mastering AI Chip Complexity: Pathways to First-Pass Silicon Success

The rapid evolution of artificial intelligence (AI) is transforming industries, from autonomous vehicles to data centers, demanding unprecedented computational power and efficiency. As highlighted in Synopsys’ guide, the global AI chip market is projected to reach $383 billion by 2032, growing at a 38% CAGR. This … Read More

Chiplet Summit 2026

All the Solutions for Developing Chiplets

2025 Keynote Addresses from Industry Leaders:

Alphawave Semi, Arm, Cadence Design Systems, Keysight, Open Compute Project, Synopsys, Teradyne

2025’s Main Topics Included:

AI/ML Acceleration, Open Chiplet Economy, Advanced Packaging Methods, Die-to-die Interfaces, Working … Read More

Chiplets: providing commercially valuable patent protection for modular products

Many products are assembled from components manufactured and distributed separately, and it is important to consider how such products are manufactured when seeking to provide commercially valuable patent protection. This article provides an example in the field of computer chip manufacture.

Chiplets

A system-on-a-chip

Chiplets and Cadence at #62DAC

Using chiplets is an emerging trend well-covered at #62DAC and they even had a dedicated Chiplet Pavilion, so I checked out the presentation from Dan Slocombe, Design Engineering Architect in the Compute Solutions Group at Cadence. In a short 20 minutes Dan managed to cover a lot of ground, so this blog will summarize the key points.… Read More

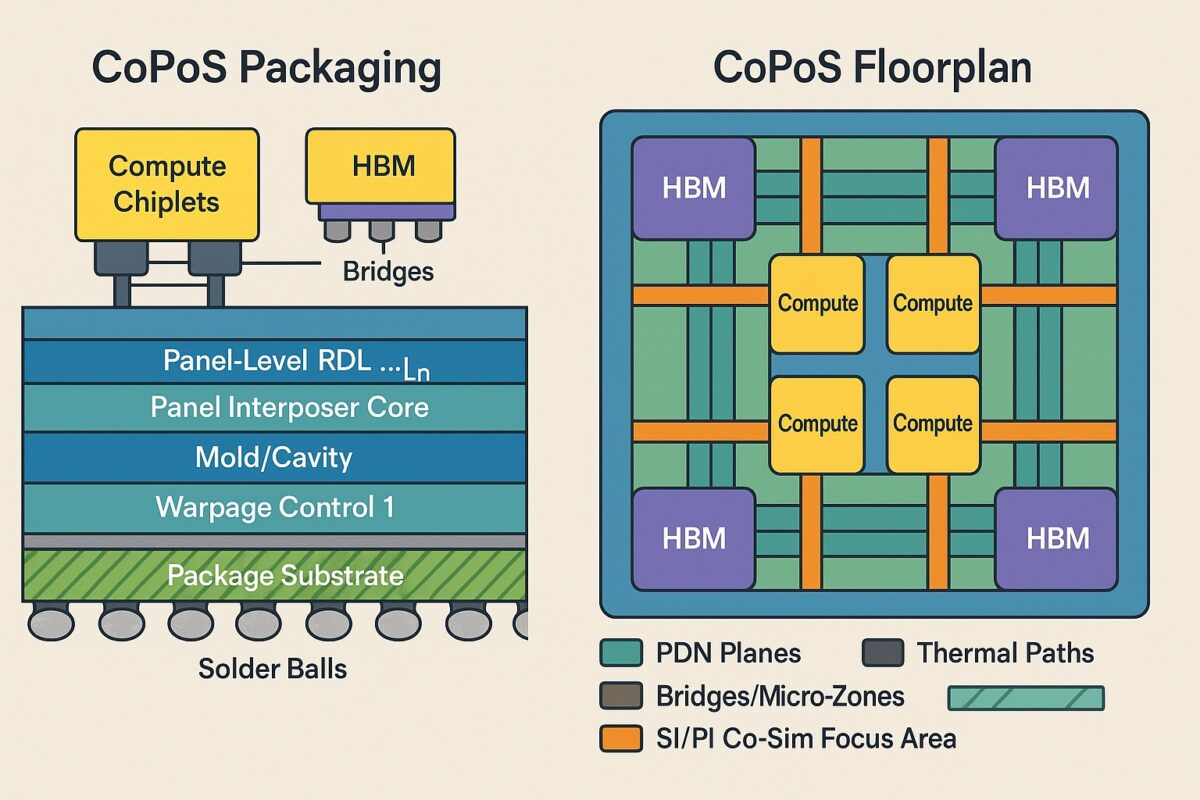

CoPoS is a Bigger Canvas for Chiplets and HBM

AI-Driven Chip Design: Navigating the Future

On July 9, 2025, a DACtv session by Dr. Peter Levin explored the transformative impact of artificial intelligence (AI) on chip design, as presented in the YouTube video. The speaker, an industry expert, delved into how AI is reshaping electronic design automation (EDA), addressing the escalating complexity of modern chips and… Read More

CEO Interview with Bob Fung of Owens Design

Bob Fung is the CEO of Owens Design, a Silicon Valley company specializing in the design and build of complex equipment that powers high-tech manufacturing. Over his 22-year tenure, Bob has led the development of more than 200 custom systems for world-class companies across the semiconductor, biomedical, energy, and emerging… Read More

AI Booming is Fueling Interface IP 23.5% YoY Growth

AI explosion is clearly driving semi-industry since 2020. AI processing, based on GPU, need to be as powerful as possible, but a system will reach optimum only if it can rely on top interconnects. The various sub-system need to be interconnected with ever more bandwidth and lower latency, creating the need for ever advanced protocol… Read More

Siemens EDA Unveils Groundbreaking Tools to Simplify 3D IC Design and Analysis

In a major announcement at the 2025 Design Automation Conference (DAC), Siemens EDA introduced a significant expansion to its electronic design automation (EDA) portfolio, aimed at transforming how engineers design, validate, and manage the complexity of next-generation three-dimensional integrated circuits (3D ICs).… Read More