I wrote recently on ANSYS and TSMC’s joint work on thermal reliability workflows, as these become much more important in advanced processes and packaging. Xilinx provided their own perspective on thermal reliability analysis for their unquestionably large systems – SoC, memory, SERDES and high-speed I/O – stacked within a … Read More

Tag: chip-package-system

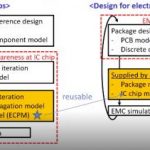

Getting to EMC Compliance by Design

At the risk of highlighting my abundant lack of expertise in the domain, I had always viewed EMC (electromagnetic compatibility) compliance and testing as one of those back-end exercises that can only be done on the real device and depends on a combination of expertise and brute-force in chip/package/module/system design (decaps,… Read More

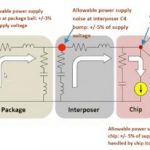

Power Integrity from 3DIC to Board

The semiconductor industry has built decades of success on hyper-integration to increase functionality and performance while also reducing system cost. But the standard way to do this, to jam more and more functionality onto a single die, breaks down when some of the functions you want to integrate are built in different processes.… Read More

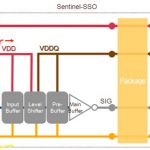

Apache on Signal Integrity

Matt Elmore has a two-part blog about the growing complexity of signal integrity analysis, both on the chip itself and the increasingly complex analysis required to make sure that signals (and power) get in and out of the chip from the board cleanly, especially to memory, which requires simultaneous analysis of chip-package-system… Read More

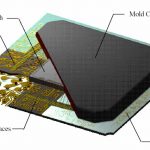

Chip-Package-System workshops

Chips, packages and circuit boards (systems, hence CPS) used to be three separate domains with their own tools that barely interacted at all. If you were lucky, reassigning a pin on a package wouldn’t have to be done manually in all 3 places. But now, from a signal integrity, noise, power point of view these three domains must… Read More