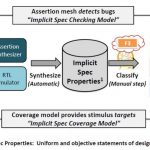

Assertion Synthesis is a new tool for verification and design engineers that can be used with simulation or emulation. At DVCon Yuan Lu of Atrenta is presenting a tutorial on Atrenta’s BugScope along with John Henri Jr of Cadence explaining how it helps emulation and Baosheng Wang of AMD discussing their experiences of the… Read More

Tag: cadence

Cadence Sigrity, Together At Last

In July Cadence acquired Sigrity, one of the leaders in PCB and IC packaging analysis. Until a decade ago, signal integrity and power analysis was something that only IC designers needed to worry about. For all except the highest performance boards, relatively simple tools were sufficient. Provided you hooked up the pins on all… Read More

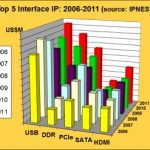

Cosmic Circuits acquisition by Cadence: IP battle with Synopsys has officially started!

If you have missed the announcement that Cosmic Circuits has been acquired by Cadence, dated February 7, you may want to read this PR. In any case, by reading this article you will understand why this acquisition is ringing the start of the “IP battle” between cadence and Synopsys. Let me remind you that I said in Semiwiki last September… Read More

Common Platform Technology Forum February 5th 2013 Live or Online!

Can’t make it to Santa Clara? Join us online!

The detailed 2013 CPTF agenda is now up in preparation for the February 5th event at the Santa Clara Convention Center. This is one of the rare times that you can get a free lunch! Watch this quick video to see what is in store for us this year. Dr. Paul McLellan and I will be there so please… Read More

Building Energy-Efficient ICs from the Ground Up

My oldest son just upgraded Smart Phones from a 3″ display to a 4.5″ display and was shocked to discover that his battery barely lasted 8 hours, so I welcomed him to the reality of limited battery life in modern SoC-based mobile devices. There is some hope in increasing battery life for our consumer-oriented devices … Read More

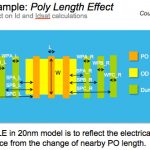

Virtuoso is 20nm-ready

I already talked about how Cadence is splitting Virtuoso into two. Anyway, it is now officially announced. The 6.1 version will continue to be developed as a sort of Virtuoso classic for people doing designs off the bleeding edge that don’t require the new features. And a new Virtuoso 12.1 intended for people doing 20nm and… Read More

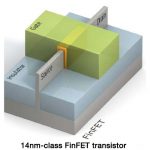

Cadence, Synopsys, and Mentor on FinFETs

In my opinion, FinFETs will be the most significant piece of technology we, as semiconductor ecosystem people, will experience this decade. Seriously this is exciting stuff and one of the top search terms on SemiWiki for 6 months running. Here is a quick peek at what the top EDA companies will be talking about at the Common Platform… Read More

What did CES 2013 mean for #SemiEDA?

CES is the preeminent gadget show, and in the LVCC South Hall a wave has been building for some time. It’s now the place where chipsets are introduced, and this year saw a wide range of introductions from Atmel, Bosch, Broadcom, Intel (OK, they’re still in Central Hall), InvenSense, Marvell, NVIDIA, Qualcomm, Samsung, ST-Ericsson,… Read More

Yawn… New EDA Leader Results Are Coming

We will soon start to see the quarterly financial reporting installments of the “Big 3” public EDA companies. I predict they will be as boring as usual. I am not sure if I would want it any differently though.

Back in the 90s there were times when it was truly interesting to wait to see what Cadence, Mentor, or later Synopsys, might announce.… Read More

Buying DDRn Controller IP AND Memory Model to the same IP vendor gives real TTM advantage

We all know the concept of “one stop shop”, becoming popular in the Design IP market. The topic we will address today is NOT the “one stop shop”, even if it looks similar, but rather that we could call “consistent design flow”.

What does that means? Simply that, if your SoC design is integrating a DDRn (LPDDR2, DDR3 or even DDR4, let’s… Read More