Intermediate representations (IRs) between high level languages (C++, AI, etc.) and machine language are both commonplace (witness LLVM) and a continuing active area of research. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford,… Read More

Tag: bernard murphy

Turnkey Multi-Protocol Wireless for Everyone

There is no IoT without wireless. If you have a great idea for a world-beating IoT device, you must integrate a wireless module (Bluetooth, Zigbee, Wi-Fi, UWB…) into that device. A ready-made companion wireless chip connected to MCU is one approach but will significantly increase unit cost and reduce profits. Products … Read More

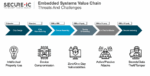

A Timely Update on Secure-IC

I last wrote about Secure IC back in 2023, a provider of embedded security technologies and services. Cadence announced at the beginning of 2025 their intention to acquire this company, which warrants a check-in again on what they have to offer. Secure-IC addresses multiple markets, from automotive, through defense/space and… Read More

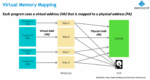

RISC-V Virtualization and the Complexity of MMUs

In the early days of RISC-V adoption, applications were microcontroller-centric with no need for virtualization support. But horizons expanded and now RISC-V is appearing in application processors, very much needing to be able to virtualize multiple apps concurrently. Take another step forward to datacenter servers running… Read More

LLMs Raise Game in Assertion Gen. Innovation in Verification

LLMs are already simplifying assertion generation but still depend on human-generated natural language prompts. Can LLMs go further, drawing semantic guidance from the RTL and domain-specific training? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO… Read More

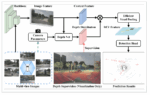

Recent AI Advances Underline Need to Futureproof Automotive AI

The world of AI algorithms continues to advance at a furious pace, and no industry is more dependent on those advances than automotive. While media and analysts continue to debate whether AI will deliver value in business applications, there is no question that it adds value to cars, in safety, some level of autonomous driving, … Read More

Perspectives from Cadence on Data Center Challenges and Trends

From my vantage point in the EDA foxhole it can be easy to forget that Cadence also has interests in much broader technology domains. One of these is in data center modeling and optimization, through their Cadence Reality Digital Twin Platform. This is an area in which they already have significant track record collaborating with… Read More

A Perspective on AI Opportunities in Software Engineering

Whatever software engineering teams are considering around leveraging AI in their development cycles should be of interest to us in hardware engineering. Not in every respect perhaps but there should be significant commonalities. I found a recent paper on the Future of AI-Driven Software Engineering from the University of … Read More

Big Picture PSS and Perspec Deployment

I met Moshik Rubin (Sr. Group Director, Product Marketing and BizDev in the System Verification Group at Cadence) at DVCon to talk about PSS (the Portable Stimulus Standard) and Perspec, Cadence’s platform to support PSS. This was the big picture view I was hoping for, following more down in the details views from earlier talks.… Read More

An Important Advance in Analog Verification

Innovation in analog design moves slowly, not from lack of desire for better methods from designers or lack of effort and ideas from design tech innovators, but simply because the space is so challenging. Continuous time and signals, and variances in ambient/process characteristics represent a multi-dimensional space across… Read More