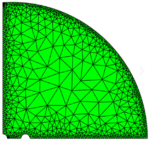

Finite element methods for analysis crop up in many domains in electronic system design: mechanical stress analysis in multi-die systems, thermal analysis as a counterpart to both cooling and stress analysis (eg warping) and electromagnetic compliance analysis. (Computational fluid dynamics – CFD – is a different beast which… Read More

Tag: bernard murphy

An Accellera Functional Safety Update

In May of 2021 Accellera released a first white paper on the challenges they hope to address with their functional safety standard, together with the scope and goals they set for themselves. One major goal in this effort has been exchange and integration of functional safety data between different tools and flow and particularly… Read More

Information Flow Tracking at RTL. Innovation in Verification

Explicit and implicit sneak paths to leak or compromise information continue to represent a threat to security. This paper looks a refinement of existing gate level information flow tracking (IFT) techniques extended to RTL, encouraging early-stage security optimization. Paul Cunningham (Senior VP/GM, Verification at … Read More

Reasoning and Planning as the Next Big Thing in AI

When I search for ‘what is the next big thing in AI?’ I find a variety of suggestions around refining and better productizing what we already know. Very understandable for any venture aiming to monetize innovation in the near term, but I am more interested in where AI can move outside the box, to solve problems well outside the purview… Read More

When Will Structured Assembly Cross the Chasm?

First, a quick definition. By “structured assembly,” I mean the collection of tools to support IP packaging with standardized interfaces, SoC integration based on those IPs together with bus fabric and other connectivity hookups, register definition and management in support of hardware/software interface definition, … Read More

5G Aim at LEO Satellites Will Stimulate Growth and Competition

Low earth orbit (LEO) satellites as an intermediary for communication became hot when Elon Musk announced Starlink (yeah, other options were available, but Elon Musk). This capability extends internet availability to remote areas and notably (for a while) to Ukraine in support of the war with Russia. Satellites can in principle… Read More

Building Reliability into Advanced Automotive Electronics

Those of you who have been in the industry for a little while will remember that the recipe for reliable electronics in cars (and other vehicles) used to be simple. Stick to old (like 10 years old) and well-proven processes and tweak rather than tear up and restart well-proven designs to the greatest extent possible. Because incrementing… Read More

ML-Guided Model Abstraction. Innovation in Verification

Formal methods offer completeness in proving functionality but are difficult to scale to system level without abstraction and cannot easily incorporate system aspects outside the logic world such as in cyber-physical systems (CPS). Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst,… Read More

Synopsys.ai Ups the AI Ante with Copilot

Last week Synopsys announced their next step in generative AI (GenAI) in Synopsys.ai Copilot based on a collaboration with Microsoft. This integrates Azure OpenAI together with existing Synopsys.ai GenAI capabilities to extend Copilot concepts to the EDA world. For those of you unfamiliar with Copilot, this is a development… Read More

Cadence Integrates Power Integrity Analysis and Fix into Design

As integration levels increase, clock frequencies rise, and feature sizes shrink it is not surprising that all or most aspects of semiconductor design become more complex and demand more from design technologies. One example where the traditional approach is breaking down is in optimizing power distribution networks (PDNs)… Read More