You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

This tutorial describes how analog IP is becoming more important in any power management strategy and shows the major analog building blocks to manage power and temperature in a SoC on leading edge technology nodes.

The tremendous demand for high-performance computing devices has led to aggressive technology scaling, allowing… Read More

ARM announced their quarterly results early this morning. ARM’s results are a funny mixture of backward looking information such as royalties which are reported a quarter late since they have to wait for their licensees to work out how many they shipped, and some very forward looking such as new licenses, which bring some… Read More

I have been at the Linley Microprocessor Conference today. This is the one that is not about mobile: about servers, networking, base-stations. Probably the most important story about the whole industry is that the “shift to ARM becomes a stampede.”

In this market it seems to be driven by the 64-bit ARMv8 instruction… Read More

Catch Mentor’s embedded sessions at ARM TechConby Beth Martin on 10-09-2013 at 9:00 amCategories: EDA

For Halloween this year, why not tell your embedded software debug horror stories at ARM TechCon? Mentor will have several campfire sessions you should consider attending, but here my Halloween thread breaks down. These three sessions are all quite cheery.

This one, Software Debug on ARM Processors in Emulationis on using emulation… Read More

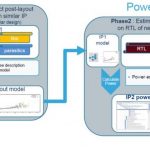

It was an interesting webinar I attended, presented by STMicroelectronicson how they are benefited in power saving and thermal dissipation by using FDSOI technology and also by using PowerArtist in their design. So, it’s an advantage from both sides – semiconductor technology and semiconductor design tool. It’s worth attending… Read More

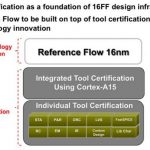

Today TSMC announced three reference flows that they have been working on along with various EDA vendors (and ARM and perhaps other IP suppliers). The three new flows are:

- 16FinFET Digital Reference Flow. Obviously this has full support for non-planar FinFET transistors including extraction, quantized pitch placement, low-vdd

…

Read More

Designing an LTE modem is an interesting case study in architectural and system level design because it is pretty much on the limit of what is possible in a current process node such as 28nm. I talked to Johannes Stahl of Synopsys about how you would accomplish this with the Synopsys suite of system level tools. He is the first to admit… Read More

At IDF Brian Krzanich gave the keynote. I won’t summarize the whole thing here but just talk about one part that was something they had actually managed to keep secret ahead of time: Quark.

Quark is a synthesizable core. It uses 1/10th power of Atom and is 1/5 size. Now I am writing this, I don’t know if this is a fair comparison… Read More

Ecosystem is everything when it comes to modern semiconductor design, especially if it is mobile. The fabless semiconductor industry has been all about ecosystem since the beginning and that is why we hold supercomputers in our hands today, believe it. After the invention of the transistor in 1947, and the invention of the integrated… Read More

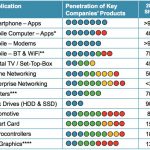

Imagination seems to be well known for a couple of things. Firstly, everyone knows that it is the graphics processor used in the iPhone and the iPad and lots of other phones. And they know that Imagination acquired MIPS at the start of this year.

But what people don’t seem to really appreciate is just what a huge portfolio of IP… Read More