Dr. Paul McLellan and I will be covering the Silicon Valley SNUG live again this year. Unfortunately we are only allowed to see the keynotes (same thing with CDNLive) but they look very good:

Keynote Address: Massive Innovation and Collaboration into the “GigaScale” Age!

Aart de Geus, Chairman and co-CEO, Synopsys, Inc.

The semiconductor industry is on the bridge to a new world of complexity empowered by smaller dimensions, new transistor types, enormous IP reuse, and a focus on the great potential of electronic systems. In other words, the GigaScale Age is upon us! In addition, our customers are facing uncertain markets where merely making a better version of their last product is not sufficient. To survive and thrive in new and unknown markets, designers and their ecosystem partners are accelerating both their innovation and their collaboration with key partners. They expect the same from their EDA, IP and services partners. In his presentation, Aart will give an overview of the enormous amount of recent innovation and collaboration happening at Synopsys as we enable “Moore’s Law plus, plus” for yet another decade!

Technology Keynote – “From Crystal Ball to Reality — The impact of Silicon IP on SoC Design”

Sir Hossein Yassaie, PhD, Chief Executive Officer, Imagination Technologies Group

SoCs have transformed the semiconductor and electronics industries, integrating staggering breadth of functionality and performance into highly cost-effective, low power but complex single-chip solution platforms. However, there has been another transformation: many of the major functional blocks on today’s SoCs are provided by Silicon IP providers rather than designed in-house. Hossein will review some of the important technological and market trends in key segments and discuss how the IP industry is helping to create the ability to translate vision into reality , and to constantly enhance it. He will touch on key functional blocks in modern SoCs explaining how the GPU is becoming the new driving force not only for modern applications but also for design methodologies and process technologies, and how heterogeneous processing is transforming the way SoCs handle key user applications such as UI’s, gaming, multimedia and more.

Technology Keynote – “Collaborate to Innovate – A Foundry’s Perspective on Ecosystem“

Dr. Cliff Hou, Vice President, Research & Development, TSMC

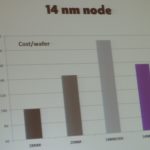

Ecosystem refers to a symbiotic, co-dependent, co-evolutionary and multiplicative relationship among its constituents. The semiconductor industry represents one of the largest business ecosystems in the world where the collective diversity and creativity has fundamentally reshaped the human society. As process scaling continues toward the atomic level, challenges abound and stakes are never higher. In this talk, we will offer a foundry perspective of the semiconductor ecosystem and how, through close collaboration, we combine individual specialties and resources to innovate and move the industry forward. Specifically, we will discuss how the collaboration with EDA is becoming ever closer, earlier and wider to enable designs concurrently with process development, even especially at the advanced nodes.

SNUG Around the world:

[TABLE]

|-

| Silicon Valley

| March 25-27, 2013

|-

| Boston

| September 12, 2013

|-

| Austin

| September 18, 2013

|-

| Canada

| October 1, 2013

|-

| Germany

| May 14, 2013

|-

| United Kingdom

| May 16, 2013

|-

| France

| June 11, 2013

|-

| Israel

| June 18, 2013

|-

| India

| June 12-13, 2013

|-

| Japan

| July 12, 2013

|-

| China

| August 22, 2013

|-

| Taiwan

| August 20-21, 2013

|-

| Singapore

| August 16, 2013

|-

As I mentioned in my blog Synopsys ♥ FinFETs, Synopsys knows FinFETs so be sure to see the FinFET tracks. Paul and I also get to attend the press lunch and hopefully, like last year, an hour roundtable with Aart. It is a great experience to hang with semiconductor people wearing SemiWiki shirts and to get recognized and even photographed. My wife rolls her eyes when it happens and makes me take out the trash when I get home to keep me grounded. But seriously, we all appreciate your support and encouragement and it is a pleasure to collaborate with you.

Note: TSMC’s Dr. Cliff Hou gets a coveted keynote so clearly Synopsys loves TSMC! Cliff would be a great addition to the Synopsys board dontcha think? I will see what I can do…..

Since 1991, SNUG (the Synopsys Users Group) has represented a global design community focused on accelerating innovation. Today, as the electronics industry’s largest user conference, SNUG brings together nearly 9,000 Synopsys tool and technology users across North America, Europe, Asia and Japan. In addition to peer-reviewed technical papers and insightful keynotes from industry leaders, SNUG provides a unique opportunity to connect with Synopsys executives, Synopsys design ecosystem partners and members of your local design community. Join your fellow engineers at the SNUG in your region — you’ll leave with practical information you can use on your current projects and the inspiration to accelerate innovation.