At the recent Hot Chips conference, Intel® unveiled Clearwater Forest, its next-generation Xeon® 6 processor with efficiency cores (E-cores). The unveiling was made by Don Soltis, Xeon Processor Architect and Intel Fellow with over four decades of processor design experience and a long-standing contributor to the Xeon roadmap. Built to deliver density and energy efficiency for large-scale data centers, Clearwater Forest reflects years of architectural refinement and cutting-edge process innovation.

Efficiency at the Heart of Xeon 6

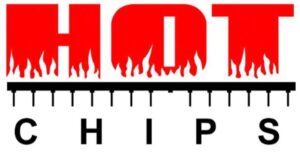

The Xeon 6 family has been designed to address a wide range of customer needs. P-core series processors target compute-intensive and AI workloads, while E-core series processors like Clearwater Forest are optimized for scale-out, high-density deployments where performance per watt and total cost of ownership are critical. Sharing a common platform foundation and software stack, the two series allow customers to mix and match without redesigning their infrastructure.

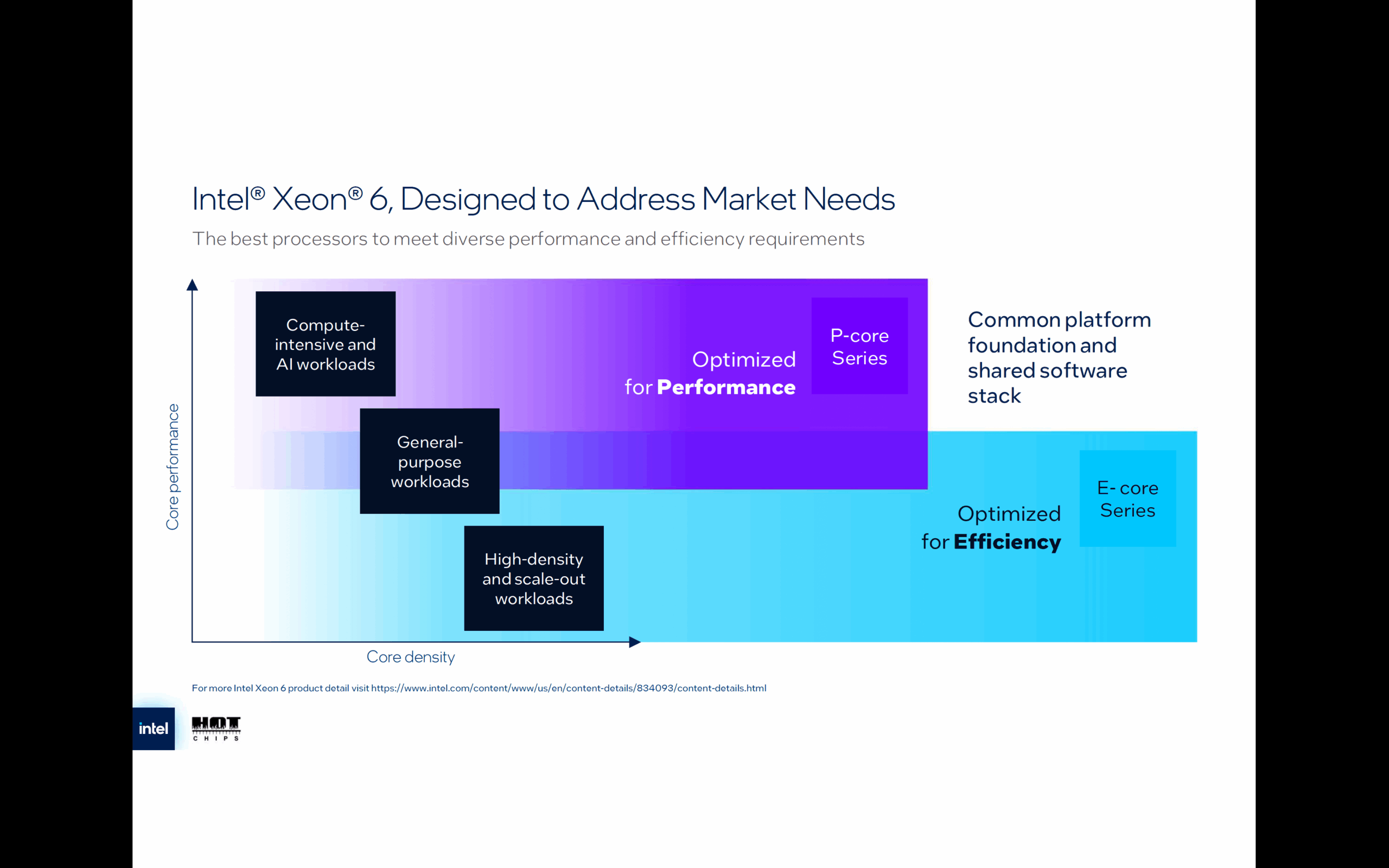

Clearwater Forest is built on Intel’s 18A process technology, which combines backside power delivery and gate-all-around transistors for better efficiency and higher density. The design reduces RC delays, lowers IR drop, and improves signal integrity, all while enabling over 90% cell utilization. Together, these advances allow Clearwater Forest to deliver more compute capability in less space with reduced power consumption.

Inside Clearwater Forest

Architectural Advancements

At the microarchitectural level, Clearwater Forest introduces significant leaps over Sierra Forest, Intel’s first-generation E-core Xeon. The front end features a 64 KB instruction cache with an on-demand length decoder for large code footprints, nine instructions per cycle via three 3-wide decoders, and deeper, more accurate branch prediction.

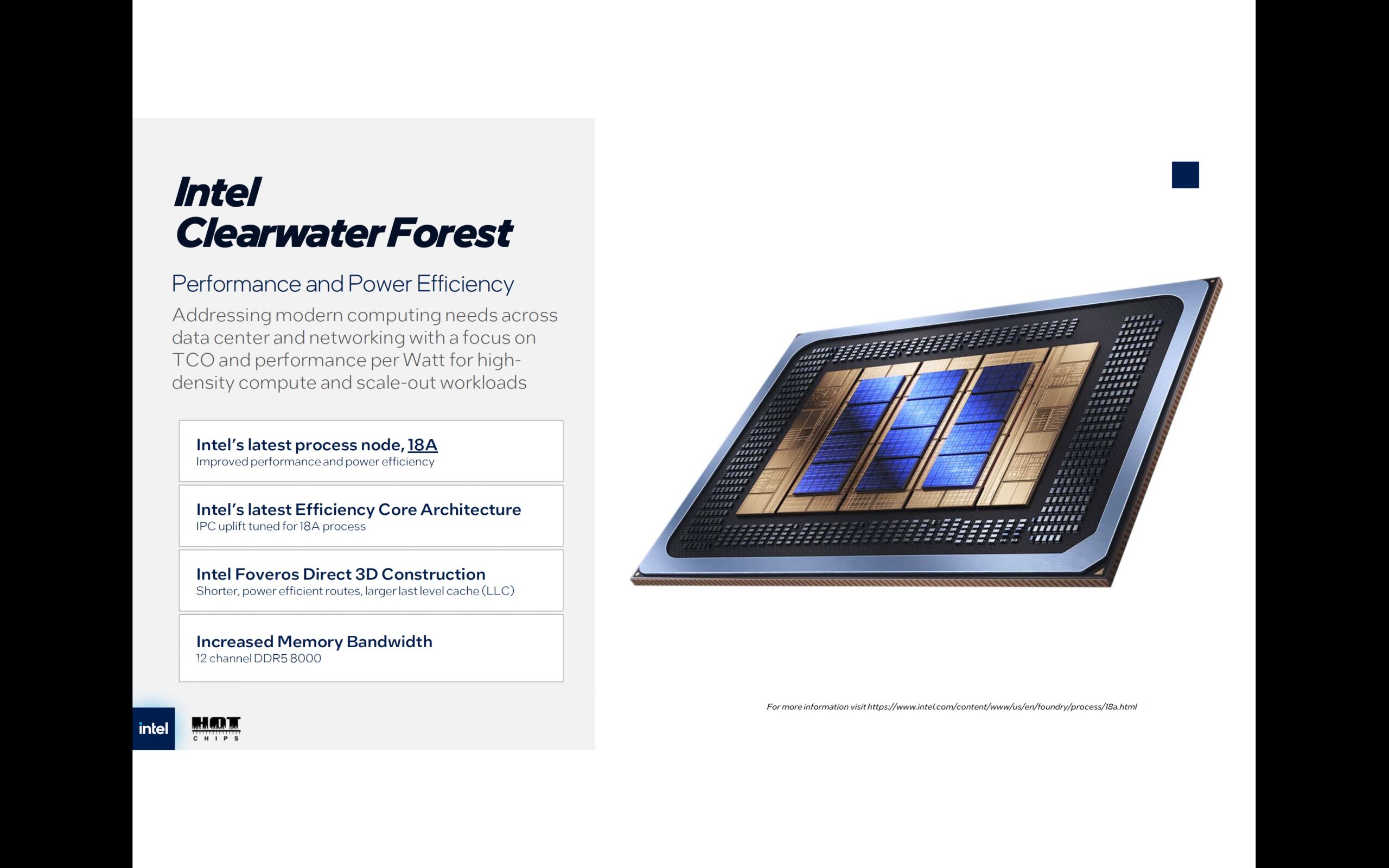

The out-of-order engine expands to eight-wide allocation and sixteen-wide retire, with a 416-entry window to uncover more data parallelism. Execution resources have been widened to 26 ports, while the execution engine itself doubles the throughput of both integer and vector operations. Load address generation improves by 1.5×, and store address generation doubles.

Memory handling is also more advanced. The subsystem supports three loads per cycle, 128 outstanding L2 misses, and sophisticated prefetchers across all cache levels. Each module consists of four cores sharing a 4 MB unified L2 cache with 17-cycle latency and twice the bandwidth of the previous generation, delivering up to 400 GB/s. Collectively, these changes result in an estimated 17% IPC uplift on SPECintRate 2017 benchmarks.

3D Chiplet Construction

Clearwater Forest makes extensive use of Intel’s Foveros Direct 3D chiplet technology, optimizing each function for the most suitable process node. The design integrates twelve CPU chiplets on Intel 18A, three base chiplets on Intel 3 for fabric, LLC, and memory controllers, and two I/O chiplets on Intel 7 for high-speed connectivity and accelerators. A monolithic mesh fabric ties everything together, with shorter interconnect routes improving both performance and power efficiency.

Performance

In a dual-socket configuration, Clearwater Forest supports 576 E-cores and 1152 MB of last-level cache. System bandwidth is equally impressive, with two sets of twelve DDR5-8000 channels delivering around 1300 GB/s read bandwidth, along with dual 96-lane PCIe 5.0 connections and 64 CXL lanes for device scalability. In addition, 144 lanes of UPI coherency provide low-latency remote memory access.

Designed for TCO and Scalability

The guiding principle behind Clearwater Forest is efficiency at scale. By enabling higher vCPU density per rack and reducing power draw, the processor allows data center operators to optimize both capital and operational expenditures. With innovations spanning process technology, microarchitecture, 3D packaging, and system-level bandwidth, Clearwater Forest sets a new benchmark for performance per watt in high-density compute deployments.

Summary

As Intel’s latest entry in the Xeon 6 family, Clearwater Forest demonstrates how architectural ingenuity and manufacturing advances can combine to deliver sustainable scaling for the most demanding cloud and enterprise workloads.

Also Read:

Revolutionizing Chip Packaging: The Impact of Intel’s Embedded Multi-Die Interconnect Bridge (EMIB)

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.