As the largest FPGA vendor, Xilinx is on top of it’s social media game by using multiple channels to talk with customers and listen. Browsing their Home page I quickly found an RSS (Really Simple Syndication) icon just below the rotating banner images, plus a link to their Blog.… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreLithography: Future Technologies

The first part of Lars Liebmann’s ICCAD keynote about lithography was on the changes in lithography that have to us to where we are today. In some ways it was an explanation of why we have the odd design rules, double patterning etc that we have in 20nm and 16nm processes. The second part of his talk was a look forward to how we might… Read More

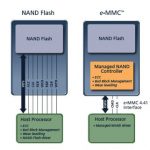

eMMC Mobile Memory

eMMC is the standard for mobile memory used in smartphones and tablets. The latest standard, released just this year, is eMMC 5.0. The previous standard, 4.51, was only released last year so things are moving quickly.

Arasan have a webinar next week to bring you up to speed on eMMC 5.0 in general and, of course, their own IP offering… Read More

Intel Bay Trail Fail II

To follow up my Bay Trail Fail blog which predicted that the leading edge Intel 22nm mobile SoC offering would fail, I must admit I was wrong. I did not think Bay Trail would see any traction in the tablet market but, as it turns out, Intel will ship 40M of those parts in 2014. Did you notice I said ship and not sell? Read on……… … Read More

Social Media at ARM

The number one semiconductor IP company in the world is ARM, and they have really figured out how to use social media in a big way to communicate with and listen to their customers. When you first visit the Home page for ARM there are four social media icons displayed in monochrome underneath the menu bar. As you hover over the icons (Twitter,… Read More

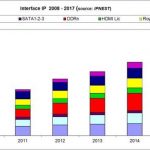

What’s new in the “Interface IP Survey” ?

The reader will find many updates in the “Interface IP Survey” from IPNEST, released in October 2013. Good question, as the IP market is a very fast moving one and the protocol based Interface IP, is moving even faster… exhibiting 20% growth rate in 2012, expected to grow with 10% CAGR between 2012 and 2017 to reach $700M. … Read More

Semiconductor Process Development: A View from the Trenches at IEDM

There is always a lot of posturing and pontificating when semiconductor executives talk about the future of process development. They are fighting an air war of perception and investor expectations, so naturally want to make sure they have plenty to brag about. But, as we pointed out recently with Intel’s problems at 14nm, moving… Read More

Front-End Design Summit: Physically Aware Design

Save closure time and boost performance by incorporating knowledge of physically aware design early into your front-end design implementation flow

With the adoption of advanced process nodes, design closure is becoming increasingly difficult due to the lack of convergence between the front end and the back end of the register-transfer… Read More

Intel’s Mea Culpa!

The Intel analyst meeting last week reads like an absolute train wreck with INTC stock dropping 5%+ the very next day. Since I work in the fabless semiconductor ecosystem during the day I was not able to listen to it live like the other pundits. Nor am I as easily fooled by Power Point slides. I did however review the materials and would… Read More

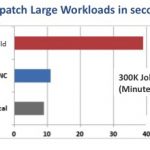

Better License Usage vs More Licenses

When you see a new product announcement from an EDA company, it is always put in terms that make it seem as if the engineer is sitting at his or her desktop with a big server and is running the new tool to wondrous effect. But the reality in the real world is that most companies have a computing infrastructure of server farms, often several… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era