You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

At DVCon Lawrence Loh and Viktor Markus Purri gave a tutorial on Formally Verifying Security Aspects of SoC Designs. Lawrence is the direector of WW application engineering and Markus is an FAE who specializes in security verification.

I’m not going to attempt to summarize an entire half-day tutorial in under 1000 words,… Read More

A few years ago my then-girlfriend was an artist and she had some friends who were in the maker movement, one who ran a tool “lending library” and so on. So she wanted to go to the Maker Faire, which is a huge event held in San Mateo exhibit center. In those days it was more like an outgrowth of burning man but there were already… Read More

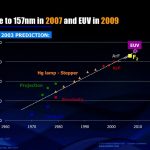

This was one of the most memorable keynotes I have seen, absolutely. Probably because it supports my belief that the infamous Intel slide that “projected” Intel will continue a linear manufacturing cost per transistor improvement at 14nm and 10nm is pure marketing fluff. Even more interesting, according to Intel, other semiconductor… Read More

There are always a number of other events that are colocated with DAC. One this year is the 23rd International Workshop on Logic and Synthesis (IWLS) that is held the weekend before DAC on May 30th and June 1st. Strictly speaking it is not colocated since it is in the Galleria Park Hotel on Sutter Street a few blocks away whereas DAC itself… Read More

I was at EDPS in Monterey the last couple of days. It is one of the most interesting conferences to attend. Go next year since you already missed it this year. It is not big but the quality of the content is high. Historically the dinner in the middle is in the Monterey Yacht Club and there is a keynote speech. A few years ago it was me but this… Read More

Had I not been briefed personally I may not have believed it. Samsung and GLOBALFOUNDRIES will work closely together on satisfying 14nm wafer demand while sharing Samsung’s FinFET secret sauce. This tells me two things: Samsung has more 14nm design wins than I had originally reported and the new GF CEO is serious about the… Read More

At the recent DVcon there was a keen focus on design verification and validation. Much of the attention is on Logic/circuit design verification, UVM, and IP verification. At the system level functional verification has improved to comprehend complex hardware and software interaction using Virtual Platforms/SystemC and Transaction… Read More

The semiconductor design sizes, these days, can easily be of the order of several hundred millions of cells, adding into the complexity of verification. Amid ever growing design sizes, it’s a must that the timing verification is done accurately. Normally Static Timing Analysis (STA) is done to check whether all clocks and signals… Read More

In his recent blog on EETimes, Kurt Shuler of Arteris took a whimsical look at the hype surrounding the IoT, questioning the overall absence of practicality and a seemingly misplaced focus on use cases at the expense of a coherent architecture. I don’t think it is all that bleak, but when it comes to architecture, Kurt is right, and… Read More

I think that the answer is pretty obvious, but the interesting point is to figure out which processor type, and which part of revenues, up-front license or royalties? One of my customers, let’s call him Mr. X, ask me to clarify this point. Mr. X has bought the excellent report from Gartner “Market Share: Semiconductor Design Intellectual… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry