by Jagadish Nayak

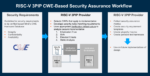

RISC-V adoption continues to accelerate across commercial and government microelectronics programs. Whether open-source or commercially licensed, most RISC-V processor cores are integrated as third-party IP (3PIP), potentially introducing supply chain security challenges that demand structured,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center