Rabin Sugumar was Distinguished Engineer and Chief Architect at Marvell/Cavium and built and led the architecture group for the ThunderX Arm server processor line. Most recently he led the architecture of the ThunderX3 processor, which had industry leading single thread performance and socket level performance at time of … Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

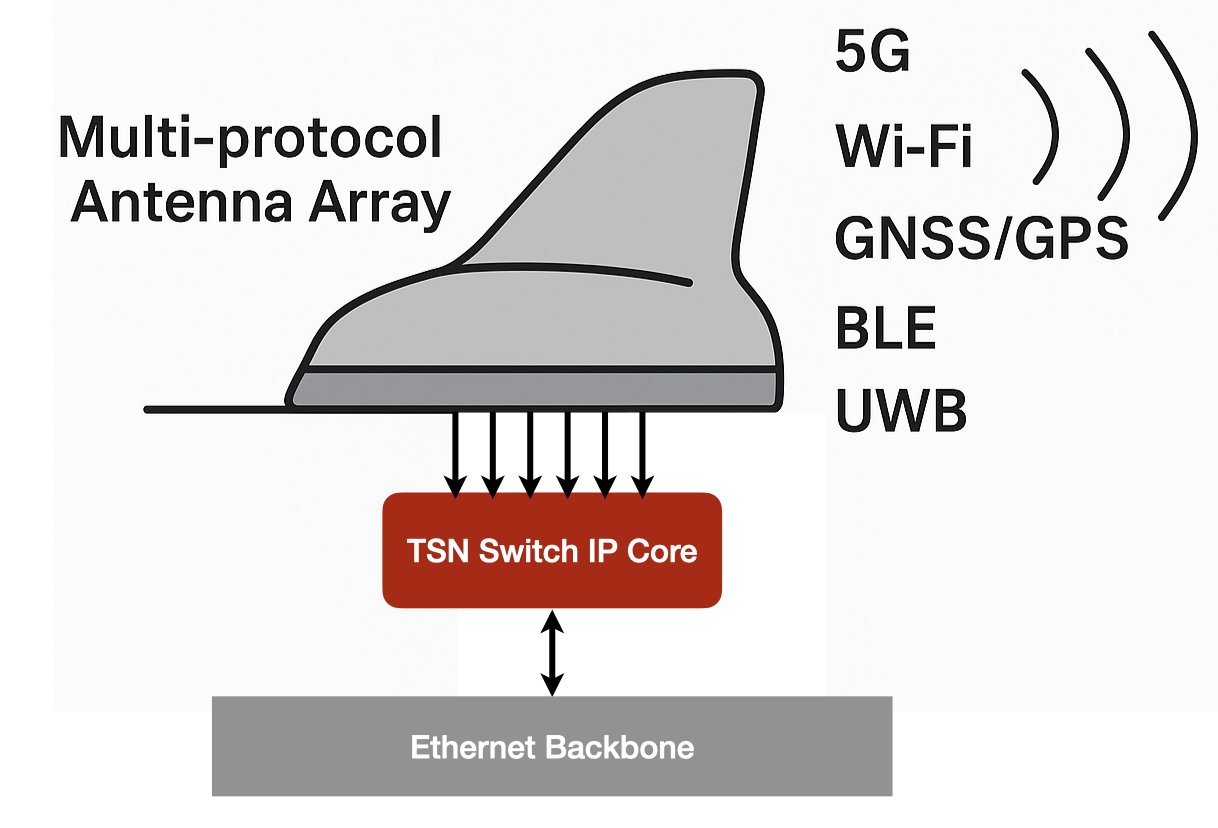

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreRANiX Employs CAST’s TSN IP Core in Revolutionary Automotive Antenna System

This press release from CAST announces a significant collaboration with RANiX Inc., highlighting the integration of CAST’s TSN Switch IP core into RANiX’s new Integrated Micro Flat Antenna System (IMFAS) SoC. This development underscores the growing adoption of Time-Sensitive Networking (TSN) in the automotive… Read More

Podcast EP306: The Challenges of Advanced AI Data Center Design with Josue Navarro

Dan is joined by Josue Navarro, product marketing engineer for Microchip’s dsPIC business unit. He began his career as a process engineer at Intel and has since transitioned into product marketing with Microchip Technology where he supports customers developing system designs utilizing Microchip’s Digital Signal … Read More

Cadence’s Strategic Leap: Acquiring Hexagon’s Design & Engineering Business

In a bold move that underscores the accelerating convergence of electronic design automation (EDA) and mechanical engineering, Cadence Design Systems announced its agreement to acquire Hexagon AB’s Design & Engineering (D&E) business for approximately €2.7 billion, equivalent to about $3.16 billion. This… Read More

TSMC 2025 Update: Riding the AI Wave Amid Global Expansion

Welcome to the second half of a very exciting year in semiconductors. While Intel and Samsung Foundry have made quite a few headlines, TSMC continues to execute flawlessly at 3nm and 2nm. With the TSMC OIP Ecosystem Forums starting later this month let’s take a look at how we got to where we are today.

Alchip’s 3DIC Test Chip: A Leap Forward for AI and HPC Innovation

Today Alchip Technologies, a Taipei-based leader in high-performance and AI computing ASICs, announced a significant milestone with the successful tape-out of its 3D IC test chip. This achievement not only validates Alchip’s advanced 3D IC ecosystem but also positions the company as a frontrunner in the rapidly evolving field… Read More

WEBINAR: Functional ECO Solution for Mixed-Signal ASIC Design

This webinar, in partnership with Easy-Logic Technology, is to address the complexities and challenges associated with functional ECO (Engineering Change Order) in ASIC design, with a particular focus on mixed-signal designs.

The webinar begins by highlighting the critical role of mixed-signal chips in modern applications,… Read More

Beyond Von Neumann: Toward a Unified Deterministic Architecture

By Thang Tran

For more than half a century, the foundations of computing have stood on a single architecture: the Von Neumann or Harvard model. Nearly all modern chips—CPUs, GPUs, and even many specialized accelerators—rely on some variant of this design. Over time, the industry has layered on complexity and specialization to… Read More

Intel Unveils Clearwater Forest: Power-Efficient Xeon for the Next Generation of Data Centers

At the recent Hot Chips conference, Intel® unveiled Clearwater Forest, its next-generation Xeon® 6 processor with efficiency cores (E-cores). The unveiling was made by Don Soltis, Xeon Processor Architect and Intel Fellow with over four decades of processor design experience and a long-standing contributor to the Xeon roadmap.… Read More

EUV Resist Degradation with Outgassing at Higher Doses

Dosing for EUV lithography walks a fine line between productivity and defectivity. Fabs can choose higher-dose exposures to suppress photon shot noise [1]. However, higher doses require EUV machines to scan the wafer at slower speeds, degrading throughput [2].

On the other hand, there is the threat of resist thickness loss that… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era