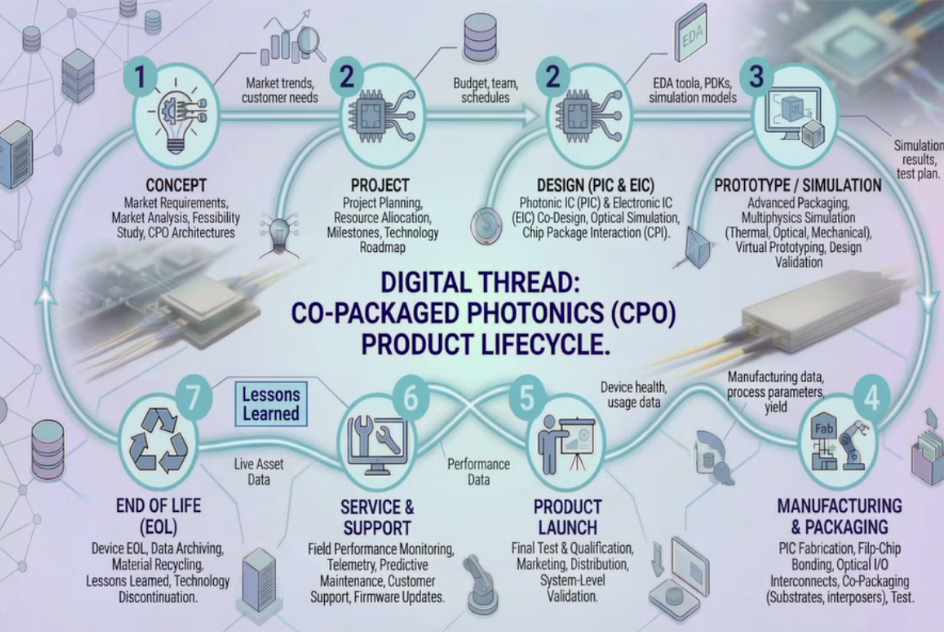

We all know the semiconductor industry is seeing a new era of data intensity. The industry’s response includes advanced semiconductor design strategies, the adoption of chiplets, and the integration of optical I/O and photonics to enable higher performance, faster AI computation, and increased modularity. Co-packaged photonics… Read More

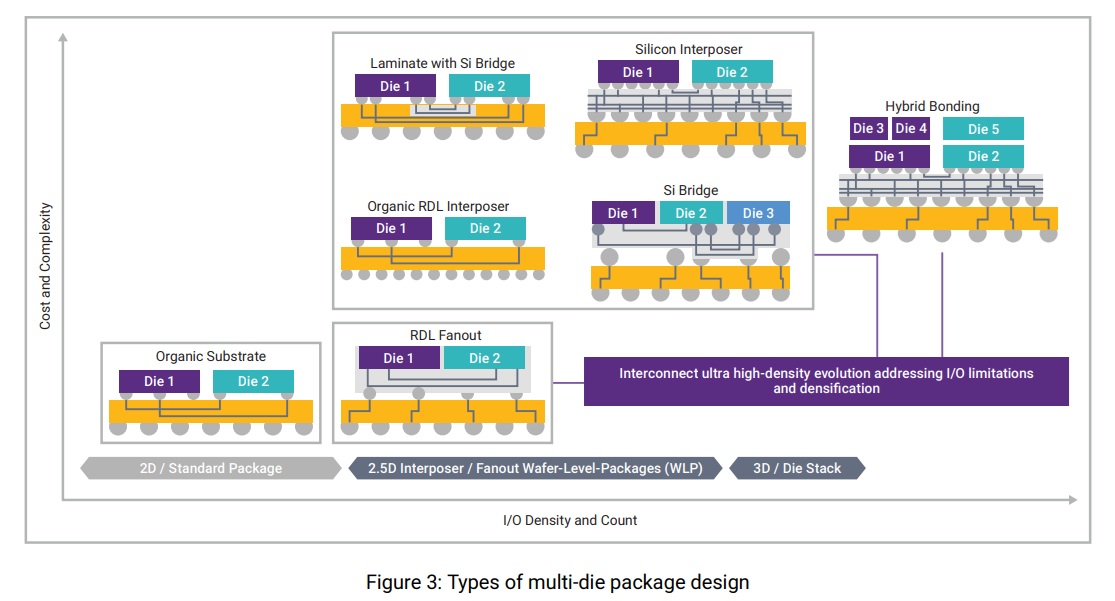

From SoC to System-in-Package: Transforming Automotive Compute with Multi-Die IntegrationModern automotive electronics are undergoing a rapid transformation…Read More

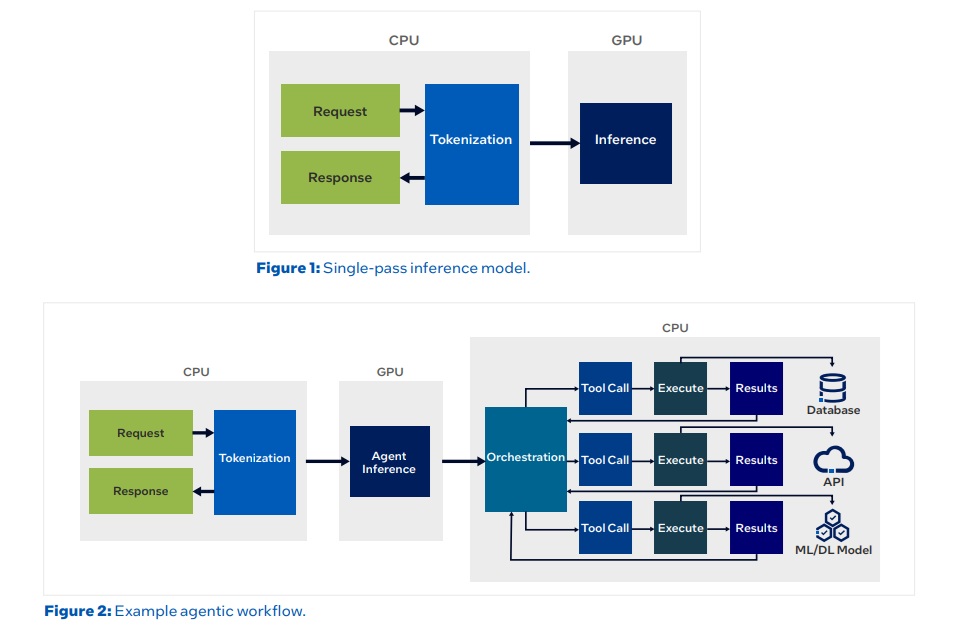

From SoC to System-in-Package: Transforming Automotive Compute with Multi-Die IntegrationModern automotive electronics are undergoing a rapid transformation…Read More Agentic AI Demands More Than GPUsAgentic AI workloads are reshaping the compute requirements…Read More

Agentic AI Demands More Than GPUsAgentic AI workloads are reshaping the compute requirements…Read More When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More

yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read MoreRISC-V Has Momentum. The Real Question Is Who Can Deliver

RISC-V has momentum. The industry knows it. The harder question is: who can actually deliver when and where it matters?

A Shift That Changes the Stakes

On March 24, 2026, Arm made something explicit: it is now a silicon company. After decades as a neutral IP provider, Arm is moving up the stack. It’s building chips and complete solutions,… Read More

CEO Interview with Jussi-Pekka Penttinen of Vexlum

Jussi-Pekka Penttinen is the chief executive officer, chief technical officer, and cofounder of Vexlum Ltd, an advanced laser technology company. With more than 15 years of experience, he is a leading researcher in the field of Vertical External Cavity Surface Emitting Laser (VECSEL) and successfully commercialized the technology.… Read More

CEO Interview with Dr. Tony Atti of Phononic

Tony Atti, Ph.D. is Phononic’s CEO. Tony is an experienced technology entrepreneur and executive, who is passionate about disruptive technology solutions that change our lives. As CEO and Co-Founder of Phononic, Dr. Atti has led the company’s mission to sustainably transform global cooling and heating through semiconductor… Read More

Podcast EP338: How Thermo Fisher Scientific Helps Advanced Semiconductor Development with Dr. Mohan Iyer

Daniel is joined by Dr. Mohan Iyer, who serves as the vice president and general manager of the Semiconductor Business Unit at Thermo Fisher Scientific, a global leader in providing reference metrology, defect characterization, and localization equipment. These advanced systems are essential for driving innovation, accelerating… Read More

Samtec’s Strong Presence at embedded world 2026

The embedded world Exhibition & Conference recently concluded. The event is held annually in Nuremberg, Germany and has become one of the most influential gatherings for the global embedded systems community. Since its inception in 2003, the event has grown from a modest technical meeting into a large-scale international… Read More

Silicon Catalyst and Microelectronics US 2026

The designation of Silicon Catalyst as the exclusive strategic partner for Microelectronics US 2026 represents a significant alignment between a leading semiconductor startup ecosystem and a rapidly growing U.S. microelectronics industry event. This partnership reflects broader trends in semiconductor innovation, … Read More

Webinar – How to Reclaim Margin in Advanced Nodes

This informative webinar discusses a significant issue that is cropping up for sub-5nm designs. As the graphic above shows, modeling uncertainty at advanced nodes results in excessive guard banding. These guard bands result in reduced performance and profit. A loss of 25 – 35% in PPA is discussed, along with the lost profit associated… Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor Technology

Alchip Technologies has recently reported significant progress in the development of advanced 2nm ASICs, positioning itself as a leader in next-generation semiconductor design for AI and HPC. The announcement highlights Alchip’s efforts to commercialize cutting-edge chip technologies and deliver highly customized … Read More

CapEx Up for Foundry, Memory

Semiconductor Intelligence estimates total semiconductor industry capital spending (CapEx) was $166 billion in 2025, up 7% from 2024. We estimate 2026 CapEx will be $200 billion, up 20% from 2025. TSMC was the largest spender in 2024 with $40.9 billion in CapEx, 25% of the total. TSMC projects 2026 CapEx will be between $52 billion… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea