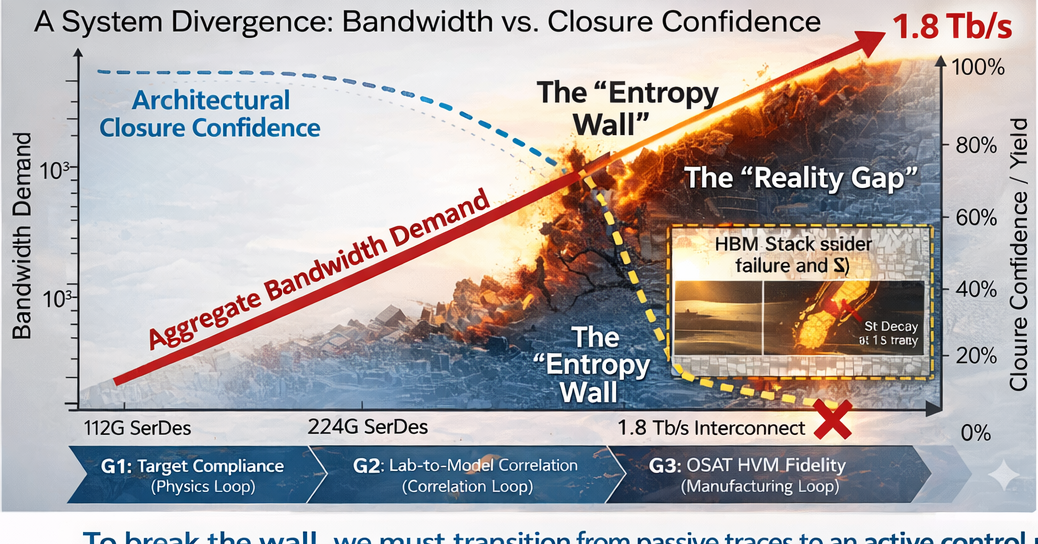

The 1.8 Tb/s inflection point is not just a bandwidth story. It is a closure story.

As AI and chiplet platforms scale, bandwidth demand continues rising — but conventional interconnect closure confidence does not rise with it. Instead, it begins to collapse under the combined weight of parasitic coupling, manufacturing drift, and assembly reality.

That is where the Entropy Wall appears.

And that is where the Reality Gap begins to widen.

At 1.8 Tb/s, the challenge is no longer only signaling speed. The real bottleneck is whether architecture intent, measured behavior, and manufacturing outcomes can still converge with confidence.

This is why I believe the industry needs to move beyond passive trace thinking and toward a more governed model:

#AdvancedPackaging #Chiplets #Semiconductor #HeterogeneousIntegration #SignalIntegrity #Packaging

As AI and chiplet platforms scale, bandwidth demand continues rising — but conventional interconnect closure confidence does not rise with it. Instead, it begins to collapse under the combined weight of parasitic coupling, manufacturing drift, and assembly reality.

That is where the Entropy Wall appears.

And that is where the Reality Gap begins to widen.

At 1.8 Tb/s, the challenge is no longer only signaling speed. The real bottleneck is whether architecture intent, measured behavior, and manufacturing outcomes can still converge with confidence.

This is why I believe the industry needs to move beyond passive trace thinking and toward a more governed model:

- Packaging as the control plane

- EM corridors as the physical leg

- SEGA™ as the convergence framework

#AdvancedPackaging #Chiplets #Semiconductor #HeterogeneousIntegration #SignalIntegrity #Packaging