There’s no denying that verification now leads the field in agentic AI announcements, accelerating the trend around this significant contribution to design automation. Siemens have just announced their Questa One Agentic Toolkit, their response to this trend, building on the core Questa One platform. Questa One provides … Read More

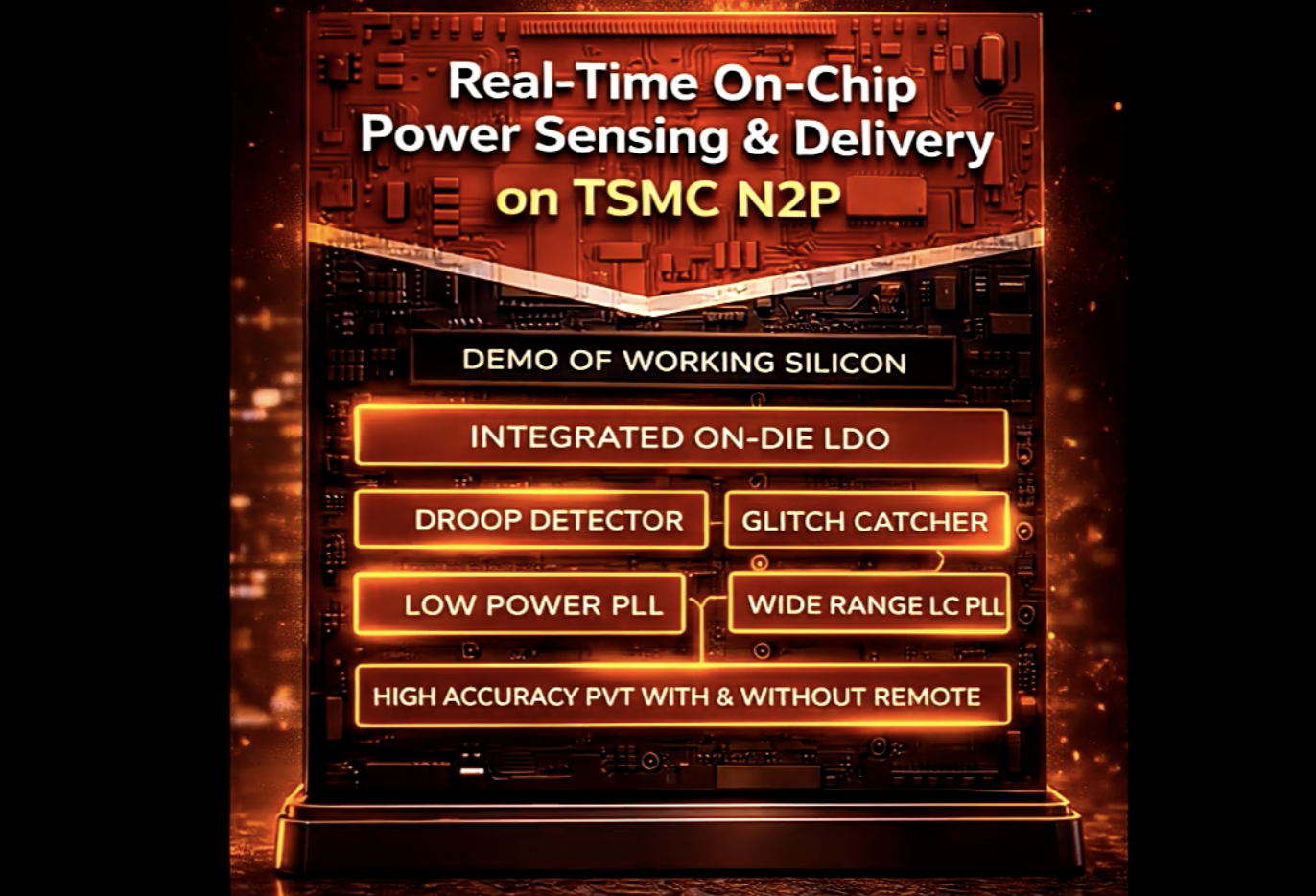

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More

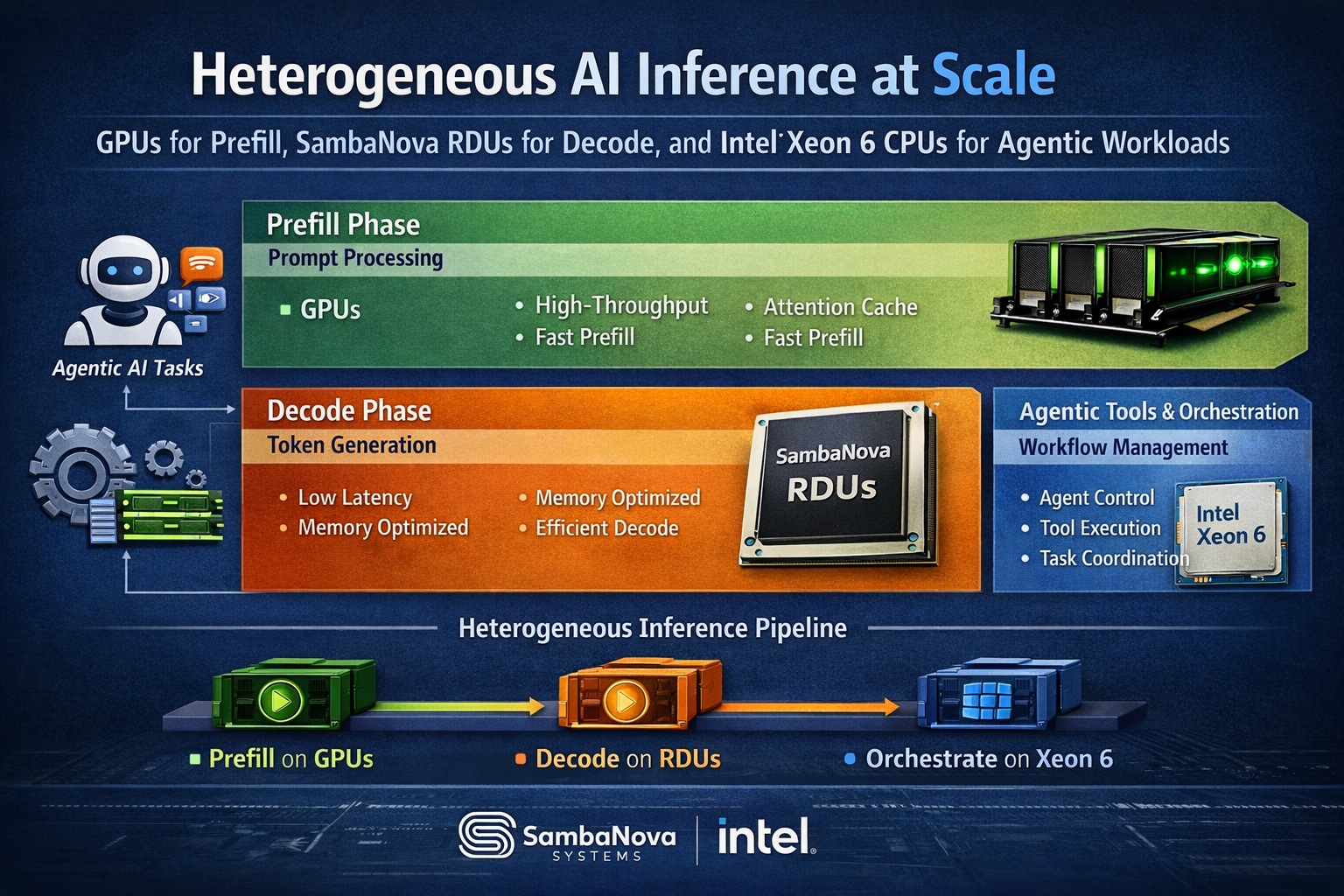

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More

CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More

TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read More

Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read MoreFunctional Safety Analysis of Electronic Systems

Safety engineers, hardware designers and reliability specialists in safety-critical industries like automotive, aerospace, medical device and industrial automation use FMEDA (Failure Modes, Effects and Diagnostic Analysis). ISO 26262 compliance for ADAS, braking systems and ECUs require FMEDA in the automotive sector.… Read More

RVA23 Ends Speculation’s Monopoly in RISC-V CPUs

RVA23 marks a turning point in how mainstream CPUs are expected to scale performance. By making the RISC-V Vector Extension (RVV) mandatory, it elevates structured, explicit parallelism to the same architectural status as scalar execution. Vectors are no longer optional accelerators bolted onto speculation-heavy cores.… Read More

Perforce and Siemens Collaborate on 3DIC Design at the Chiplet Summit

The recent Chiplet Summit at the Santa Clara Convention Center was buzzing with many enabling technologies for chiplet-based design. Collaboration was also on display during many parts of the show. A presentation in the Siemens booth was a perfect example of both of those trends. In the Siemens booth, Perforce presented an excellent… Read More

Building the Interconnect Foundation: Bump and TSV Planning for Multi-Die Systems

The first article in this series examined how feasibility exploration enables architects to evaluate multi-die system configurations while minimizing early design risk. Once architectural decisions are validated, designers must translate conceptual connectivity requirements into physical interconnect infrastructure.… Read More

CHERI: Hardware-Enforced Capability Architecture for Systematic Memory Safety

The rapid escalation of cyberattacks over the past two decades has exposed a fundamental weakness at the core of modern computing systems: the lack of memory safety. Industry data consistently shows that the majority of critical software vulnerabilities stem from memory corruption issues such as buffer overflows, use-after-free… Read More

WEBINAR: Two-Part Series on RF Power Amplifier Design

At lower frequencies with simpler modulation, RF power amplifier (PA) designers could safely concentrate on a few primary metrics – like gain and bandwidth – and rely on relaxed margins to ensure proper operation in a range of conditions. Today’s advanced RF PA design is a different story. mmWave and sub-THz frequencies introduce… Read More

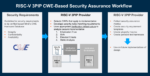

Securing RISC-V Third-Party IP: Enabling Comprehensive CWE-Based Assurance Across the Design Supply Chain

by Jagadish Nayak

RISC-V adoption continues to accelerate across commercial and government microelectronics programs. Whether open-source or commercially licensed, most RISC-V processor cores are integrated as third-party IP (3PIP), potentially introducing supply chain security challenges that demand structured,… Read More

Apple’s iPhone 17 Series 5G mmWave Antenna Module Revealed to be Powered by Soitec FD-SOI Substrates

Recent independent teardown and technical analyses have confirmed that the 5G mmWave antenna module powering Apple’s latest iPhone 17 lineup relies on advanced SOITEC based Fully Depleted Silicon-On-Insulator (FD-SOI) substrate technology. The discovery highlights a significant architectural shift in high-frequency… Read More

Another Quantum Topic: Quantum Communication

In my recent series on quantum computing (QC), I intentionally overlooked a couple of adjacent topics: quantum communication and quantum sensing. These face some of the same challenges as QC, however I noticed a recent report on a test quantum network implemented by Cisco and Qunnect which led me to find more from Cisco on their … Read More

Is Intel About to Take Flight?