Because of its open and modular nature, RISC-V has faced recognizable security challenges stemming from fragmentation, performance inefficiencies, and inherent vulnerabilities. Fragmentation across implementations leads to inconsistencies, making it difficult to enforce uniform security measures. Performance inefficiencies can introduce timing side-channel attacks, where attackers exploit execution time variations to extract sensitive data. Additionally, security vulnerabilities such as Jump-Oriented Programming (JOP) attacks and buffer overflow exploits have demonstrated RISC-V-based systems weaknesses. Addressing these risks has been a crucial focus in the ongoing development of the RISC-V Privileged Specification and supporting architectural innovations.

Recent Architectural Innovations

RISC-V’s privileged specification has faced challenges related to fragmentation, performance inefficiencies, and security vulnerabilities—factors that impact OS support, virtualization, and memory protection. However, recent progress in the RISC-V Privileged Specification has addressed many of these issues, bringing it closer to the robustness of proprietary ISAs like ARM and x86. In parallel, new architectural innovations are further strengthening RISC-V’s capabilities by introducing improvements in memory management, scheduling, and execution efficiency.

As of March 6, 2025, the RISC-V Privileged Architecture Specification version 1.13 has successfully completed its public review process and has been ratified. The 30-day public review period, which started on September 3, 2024, and concluded on October 1, 2024, allowed stakeholders to provide feedback and suggest improvements. Following this review, the specification underwent necessary revisions and was officially ratified. This ratification marks a significant milestone in addressing previous challenges related to fragmentation and security vulnerabilities within the RISC-V ecosystem. With a more stable foundation for operating system support, virtualization, and memory protection, the updated specification enhances RISC-V’s position in modern computing.

Connections Between v1.13 and Recent Patented Innovations

The RISC-V Privileged Architecture Specification v1.13 introduces refinements to privilege levels, memory protection, hypervisor support, and exception handling to strengthen security and performance. One of the most significant refinements in v1.13 is improvements to Hypervisor Mode (H-Mode), which enables more efficient virtual machine (VM) scheduling and reduces execution delays in privileged mode. A related patented innovation, Time-Based Scheduling for Extended Instructions, enhances this feature by optimizing how privileged instructions are scheduled, ultimately reducing context-switch latency. The direct connection between these two advancements is clear: while v1.13 provides the foundation for better hypervisor management; time-based scheduling ensures that hypervisor instructions execute more efficiently. A hypervisor running on a v1.13-compliant RISC-V processor would benefit from reduced instruction stalls and improved VM performance, allowing for smoother virtualization workloads.

Another area where v1.13 and recent innovations align is in memory protection. The specification expands Physical Memory Protection (PMP) and refines virtual memory management to improve access security. Together, these improvements ensure that while v1.13 enforces stricter security policies for memory access, load prediction ensures that privileged memory operations execute efficiently within those constraints. This is particularly important for real-time operating system (OS) environments and security-sensitive applications, where low-latency memory access is crucial to performance and stability.

Additionally, v1.13 introduces refinements to Machine Mode (M-Mode) and Supervisor Mode (S-Mode) execution, making privileged execution more predictable and structured. These updates align with another patented innovation, Out-of-Order Execution for Loop Instructions, which allows the CPU to process system-critical loops more efficiently. The v1.13 spec defines the rules for privileged execution, while out-of-order execution enhances performance within those guidelines. A v1.13-compliant OS kernel running on a CPU that implements out-of-order execution will experience faster privilege mode loops, reducing interrupt handling delays and improving overall system efficiency.

Enhancing RISC-V Performance with Architectural Innovations

Beyond the advancements in the privileged specification, recent patented innovations are further strengthening the RISC-V ecosystem. These enhancements improve memory efficiency, scheduling, and overall execution performance, providing the level of system protection currently enjoyed by proprietary ISA offerings. One such advancement is Time-Based Scheduling for Extended Instructions, which optimizes execution timing for complex privileged instructions. This mechanism ensures smoother operating system performance and reduces bottlenecks in system-level task execution. By lowering the latency in context switching between guest virtual machines, hypervisors can operate more efficiently, leading to better virtualization performance.

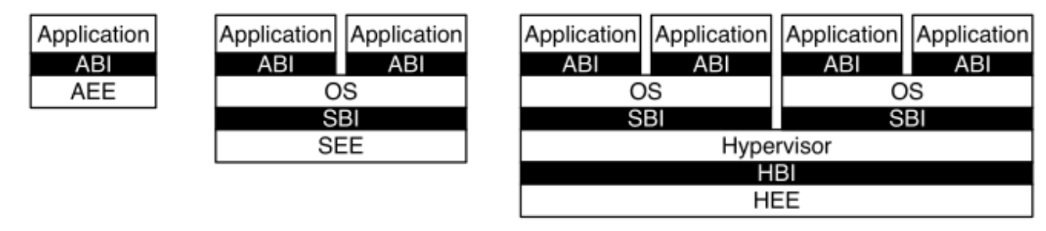

The RISC-V Privileged Specification defines a hierarchical privilege model that supports different execution environments. The figure below illustrates the layering of these privilege levels, including OS, SBI, and hypervisor support.

The RISC-V Privileged Specification defines a hierarchical privilege model that supports different execution environments. The figure below illustrates the layering of these privilege levels, including OS, SBI, and hypervisor support.

The introduction of Out-of-Order Execution for Loop Instructions has also significantly improved OS-level and hypervisor performance. This enhancement allows loop instructions to execute non-sequentially, making privileged task handling more efficient. Context switching and interrupt processing benefit greatly from this approach, as it minimizes execution stalls and increases hypervisor responsiveness.

Conclusion

By combining the ratification of the RISC-V Privileged Specification version 1.13 with architectural innovations in memory management and execution efficiency, RISC-V is making significant strides in overcoming past limitations. These advancements position it as a more competitive alternative to proprietary ISAs, paving the way for wider adoption in high-performance computing, cloud infrastructure, and secure enterprise environments.

Also Read:

Harnessing Modular Vector Processing for Scalable, Power-Efficient AI Acceleration

An Open-Source Approach to Developing a RISC-V Chip with XiangShan and Mulan PSL v2

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.