Everspin’s recent fireside chat, moderated by Robert Blum of Lithium Partners, offered a crisp look at how the company is carving out a durable niche in non-volatile memory. CEO Sanjeev Agrawal’s core message was simple: MRAM’s mix of speed, persistence, and robustness lets it masquerade as multiple memory classes, data-logging, configuration, and even data-center memory—while solving headaches that plague legacy technologies.

At the heart of Everspin’s pitch is performance under pressure. MRAM reads and writes in nanoseconds, versus microsecond-class writes for NOR flash. In factory automation, that difference is existential: robots constantly report state back to PLCs, and a sudden power loss with flash can scrap in-process work. With MRAM, the system snapshots in nanoseconds, so when power returns, machines resume exactly where they left off. The same attributes—instant writes, deterministic behavior, and automotive-grade temperature tolerance (−40°C to 125°C) translate into reliability for EV battery management systems, medical devices, and casino gaming machines (which must log every action multiple times).

Everspin organizes its portfolio into three families. “Persist” targets harsh environments and mission-critical data capture. “UNESYS” combines data and code for systems that need high-speed configuration—think FPGAs that today rely on NOR flash and suffer painfully slow updates. Agrawal’s thought experiment is vivid: a large configuration image that takes minutes on NOR could be near-instant on MRAM reboots and rollbacks included. Finally, “Agilus” looks forward to AI and edge-inference use cases, where MRAM’s non-volatility, SRAM-like speed, and low leakage enable execute-in-place without the refresh penalties and backup complexities of SRAM.

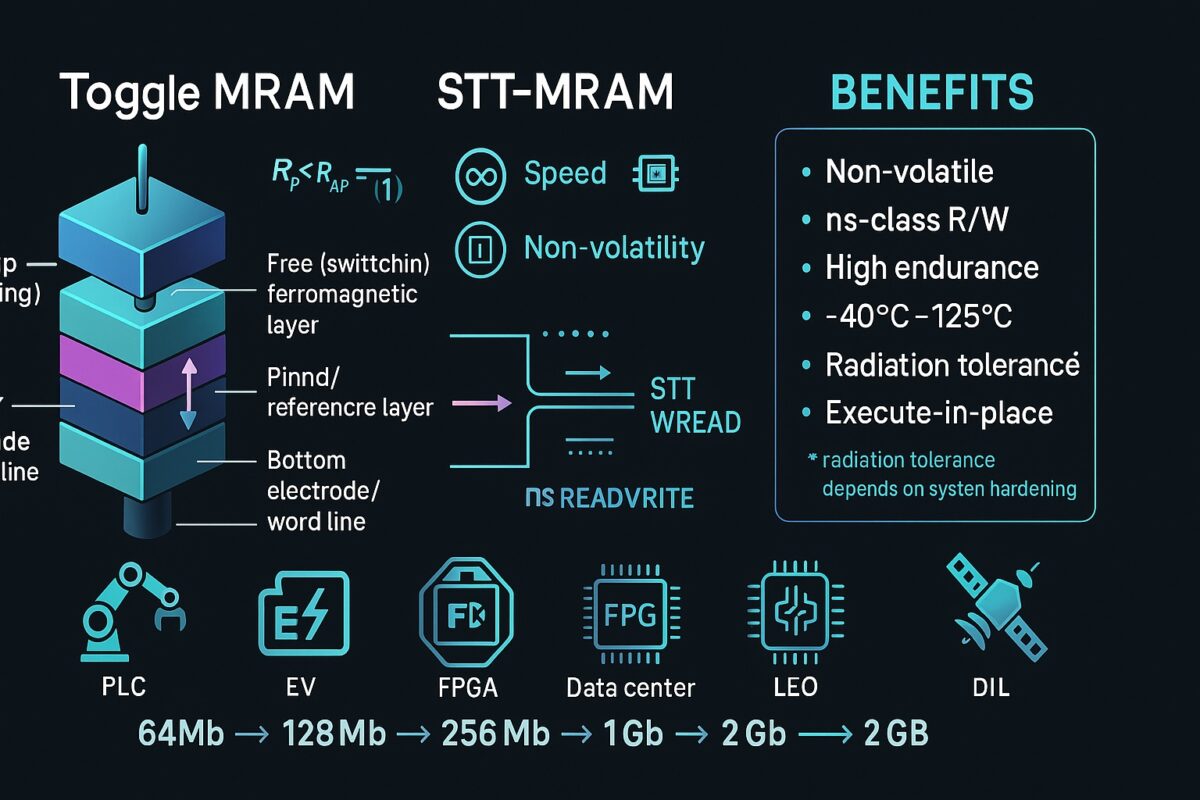

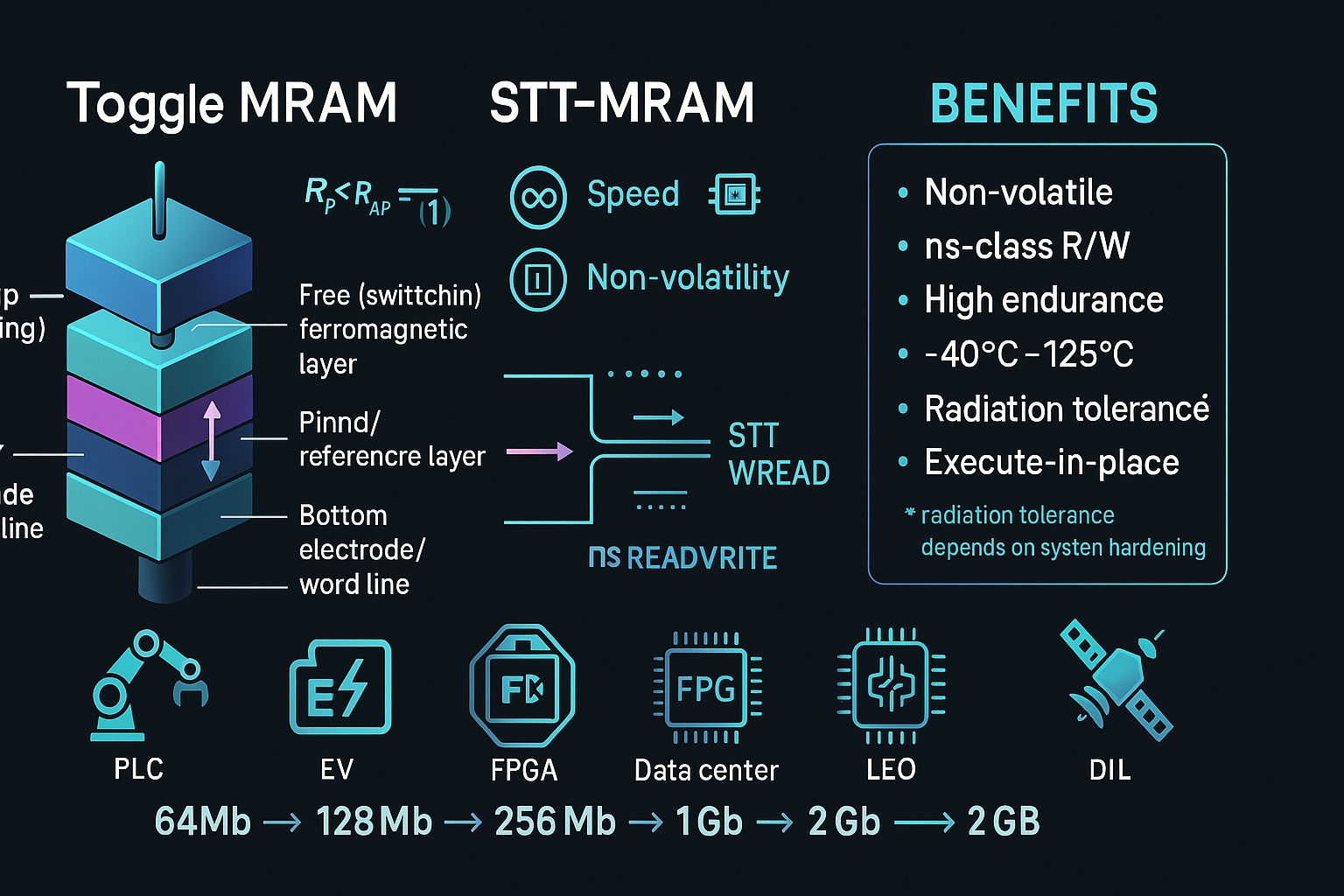

The business model is intentionally diversified: product sales; licensing and royalties (including programs where primes license Everspin IP, qualify processes, and pay per-unit royalties); and U.S. government programs that need radiation-tolerant, mission-critical memory. On the product side, Everspin ships both toggle (field-switched) MRAM and perpendicular spin-transfer torque (STT-MRAM), the latter already designed into data-center and configuration solutions. The customer base spans 2,000+ companies—from Siemens and Schneider to IBM and Juniper served largely through global distributors (about 90% of sales), with Everspin engaging directly early in the design-in cycle.

Strategically, the company sees a major opening as NOR flash stalls around the 40 nm node and tops out at modest densities. Everspin is shipping MRAM that “looks like NOR” at 64–128 Mb today, with a roadmap stepping from 256 Mb up to 2 Gb, aiming to land first high-density parts in the 2026 timeframe. Management sizes this replacement and adjacent opportunity at roughly $4.3B by 2029, and claims few credible MRAM rivals at these densities. Competitively, a South Korea–based supplier fabbed by Samsung offers a single native 16 Mb die (binned down to 4 Mb) with a longer-dated jump to 1 Gb, while Avalanche focuses on aerospace/defense with plans for 1 Gb STT-MRAM; Everspin’s pitch is breadth of densities, standard packages (BGA, TSOP), and an active roadmap.

Beyond industrial and config memory, low-earth-orbit satellites are a fast-emerging tailwind. With tens of thousands of spacecraft projected, radiation-tolerant, reliable memory is paramount; Everspin cites work with Blue Origin and Astro Digital and emphasizes MRAM’s inherent radiation resilience when paired with hardened front-end logic from primes. Supply-chain-wise, the company spreads manufacturing across regions: wafers sourced from TSMC (Washington State and Taiwan Fab 6) are finished in Chandler, Arizona; packaging and final test occur in Taiwan. For STT-MRAM, GlobalFoundries handles front end (Germany) and MRAM back end (Singapore), with final assembly/test again in Taiwan, diversifying tariff and logistics exposure.

Financially, Everspin reported another profitable quarter, slightly ahead of guidance and consensus, citing early recovery from customers’ post-pandemic inventory overhang and growing design-win momentum for its XSPI family (with revenue contribution expected in 2025). The balance sheet remains clean—debt-free with roughly $45M in cash—and the go-to-market team has been bolstered with a dedicated VP of Business Development and a new VP of Sales recruited from Intel’s Altera business.

Agrawal’s long-view is unabashed: MRAM is “the future of memory.” Whether replacing NOR in configuration, displacing SRAM at the edge for inference, or anchoring radiation-tolerant systems in space, Everspin’s thesis is that one versatile, non-volatile, fast, and power-efficient technology can simplify architectures while cutting energy use—an advantage that grows as AI workloads proliferate. If execution matches the roadmap, the company stands to be the domestic standard-bearer for MRAM across a widening set of markets.

Also Read:

Weebit Nano Moves into the Mainstream with Customer Adoption

Relaxation-Aware Programming in ReRAM: Evaluating and Optimizing Write Termination

Weebit Nano is at the Epicenter of the ReRAM Revolution

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center