Now Michael Bloomberg probably wouldn’t want FATLAB but let’s face it, to think like him you need a lot of education, alot. He may be banning 14nm because it will increase FPGAs densities and thus the consumer as well. Stay tuned. After some comments from my dear readers, one who said to watch it with respect to my harshness about AccelDSP; I needed to address this issue immediately. I actually woke up with a Virtex-II in my bed missing some pins. Yes, this is serious.

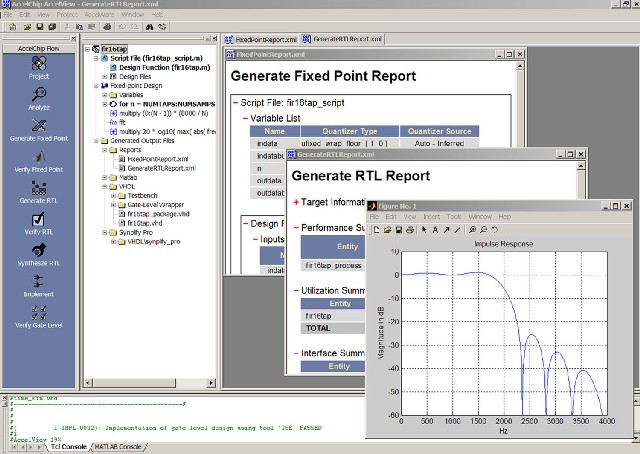

The idea behind AccelDSP was good. As a system developer, like the rest of the world, I use MATLAB or Octave. (Now don’t tell anyone about the Octave, as I’m frugal and wise, but not cheap!) MATLAB is the best systems modeling tool, period. Rhapsody, SysML, UML and the likes to model some grandiose system is never going to replace MATLAB and frankly it is another thing to do on the ever growing design checklist. The disconnect as you know is how to get that great system you have modeled in MATLAB into silicon, in particular an FPGA. Well AccelDSP tried doing that but had limitations. For me the big limitation is the one that it needed to work. You know click that magic button and bingo VHDL. True it would work for a FIR filter but for larger more nested loop structures, no worky. No floating point either and I like floating point, who doesn’t? I also enjoyed the tool hanging up for hours on end, then just going away. It had a way of making me feel productive and of course I would just sit and stare at the screen until it finished. The other issue was cost; it was like a billion dollars. ($100k+)

My earlier article about HLS being Real is true but there is still a disconnect from the modeling realm into the Silicon. MATLAB does have C Coder, which takes your MATLAB and converts to C and then Vivado HLS can work on that. I have used that path and it works but it is not ideal for obvious reasons. The major one is the penalty for abstracting a level higher. So can I make a plea with the FPGA companies? Would you consider partnering with MATLAB (besides Simulink, I know all about that, and that is not the solution either) or maybe buying MATLAB?

Every DSP house, Medical, RADAR, Automotive, Wall Street etc… USE MATLAB. I’ll share a secret with you. I cast my C from MATLAB by hand. I know, you’re saying how inefficient, how error prone Luke! What are you thinking? I know, it’s terrible and I am ashamed.If we think about it, system engineers model the design and flow down / partition the requirements to hardware (FPGAs) and software (CPU). The Modeling tool is MATLAB (Have I said that enough?). It would be orders of magnitude more efficient to flow down the model to the FPGA guys to work the ‘FATLAB’ tool instead of writing the VHDL by hand. One thing is true; the idea that we are going to hand code a 6.8 Billion transistor FPGA is totally absurd. Try it and your competition is going to blow your doors off using HLS.

But FPGAs have inherent frustrations on the programming language. CPU’s have C; FPGAs well now have C, C++, SystemC, Verilog, VHDL, (Zync) EDKs, etc… And now I want a MATLAB HLS, Again? Perhaps the group is smaller than I think but the programming of the FPGAs cannot be bird shot and MATLAB is where most start; why not leverage that correctly to synthesize, again? Ok, time to dust of AccelDSP and create FATLAB? If it existed, most I know would use it and would probably pay for it, I know I would.

lang: en_US

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center