On the Sunday evening at IEDM last year, TechInsights held a reception in which Arabinda Das and Jeongdong Choe gave presentations that attracted a roomful of conference attendees. Arabinda was first up, giving a talk on the “10-year Journey of Apple’s iPhone and Innovations in Semiconductor Technology”, followed by Jeongdong discussing “Memory Process, Design and Architecture: Today and Tomorrow”.

Arabinda gave a broad-brush look back at the sequential development of the iPhone and its feature components – we tend to forget that the first one had no camera, fingerprint sensor, face recognition, etc., so it was definitely a trip down memory lane.

Jeongdong presented a review of the latest memory technologies seen by the reverse engineering specialists, summarising their recent analyses in a fair amount of detail, and which I’d like to go through in this article. Jeongdong is a Senior Technical Fellow at the company, and their subject-matter expert for memory technology. Before joining TechInsights, he worked as a Team Lead in R&D for SK Hynix and Samsung advancing next-generation memory devices, so he knows whereof he speaks.

NAND Flash Technology

We started with a look at NAND flash, with the market shares of the top six manufacturers given as Samsung 36%, Toshiba 19%, Western Digital (WD) 15%, Micron 13%, SK Hynix 11%, and Intel 6%, as of November 2018.

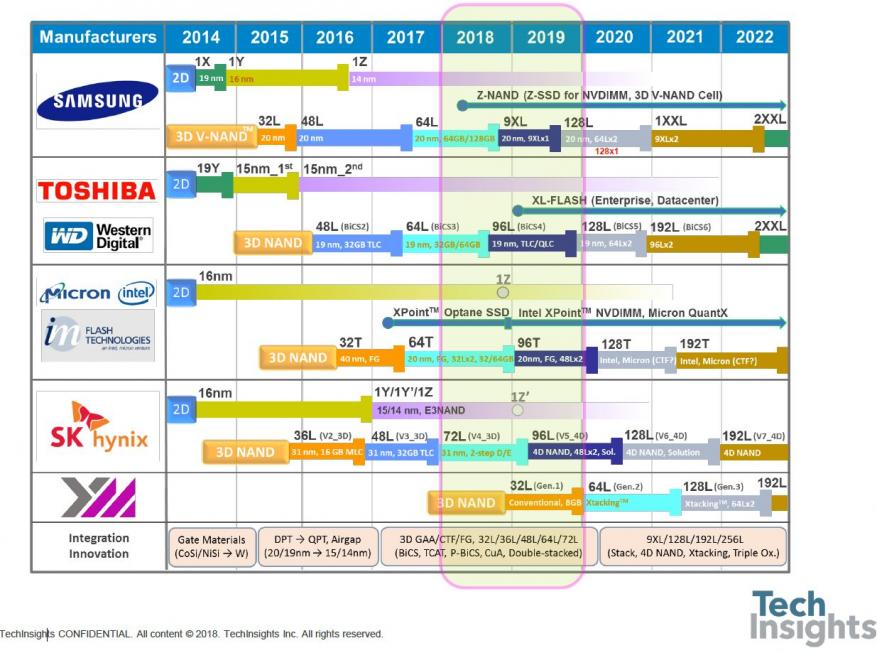

Jeongdong generates road-maps for memory every year, and below is the updated one for NAND flash. You can see that we are now into the era of 1z-nm planar flash (probably 13-14 nm, seeing as 1y was ~15 nm), and ~96 layers of 3D flash, with quadruple-level cells. The roadmap is based on published predictions, but I find it hard to believe that in a mere three years we will be getting to 200+ layers.

At the bottom of the figure is the technology evolution over the last few years, starting with the transition of the control gate from silicides to tungsten in planar devices; then we move from double patterning to quadruple patterning, as we get below 20 nm feature sizes. We see the widespread adoption of air gaps (actually, Micron started that at the 25-nm generation), and as the 15/16 nm planar parts see full production, the 3D/V-NAND products are launched. Those use two storage technologies, charge-trap (storing the charge on a silicon nitride layer – Samsung, Toshiba/WD, and SK Hynix), and floating gate (Micron/Intel).

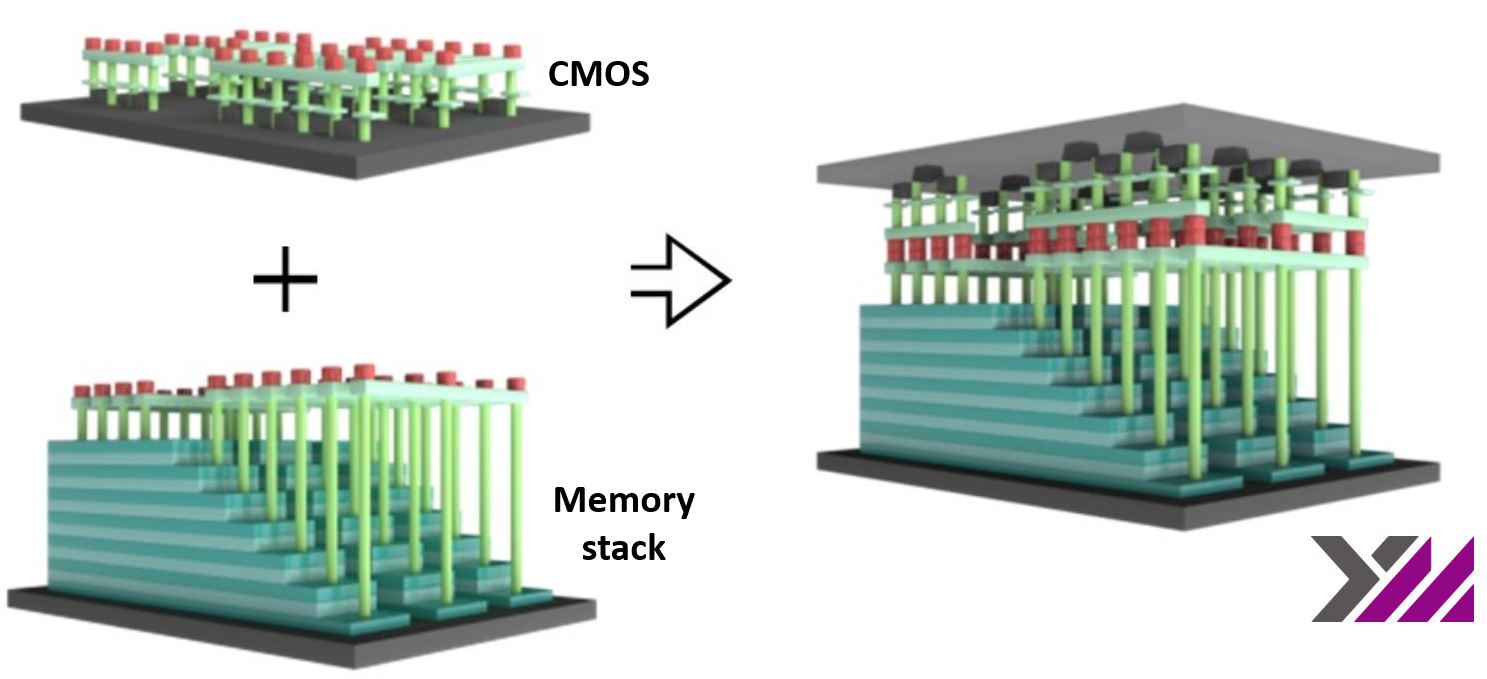

Micron/Intel also used a different layout philosophy which gave a greater areal data density; they engineered the stack to have the drive circuitry under the array, saving peripheral area, and making the die smaller – dubbed by them as CMOS-under Array (CuA). Their 64-layer product is a 2x 32 stack, and the 96-layer uses 2x 48-layer stacks.

Looking to the future, the roadmap shows up to 256 layers, and planar will fade out except for niche applications. “4D NAND” appears to be the SK Hynix version of CuA, and Xtacking is the YMTC (Yangtze Memory Technologies Co.) process of stacking CMOS over the array to save area.

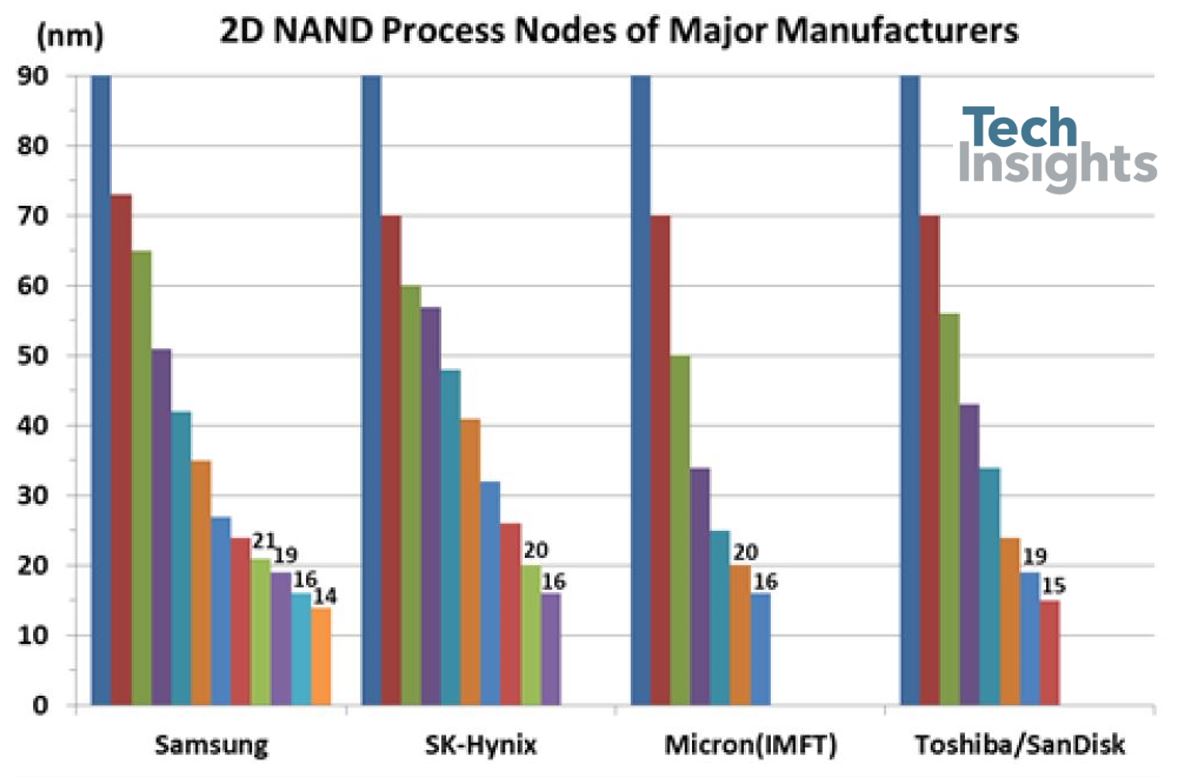

Tracking the planar devices, we have this sequence from the major manufacturers:

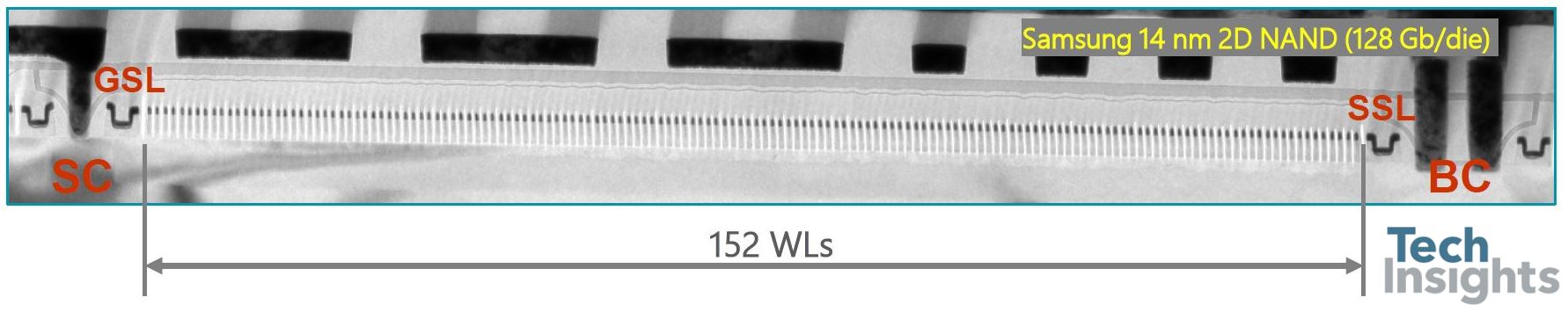

The smallest half-pitch seen so far is the Samsung 14-nm 128-Gb die, with a block size of 152 cells:

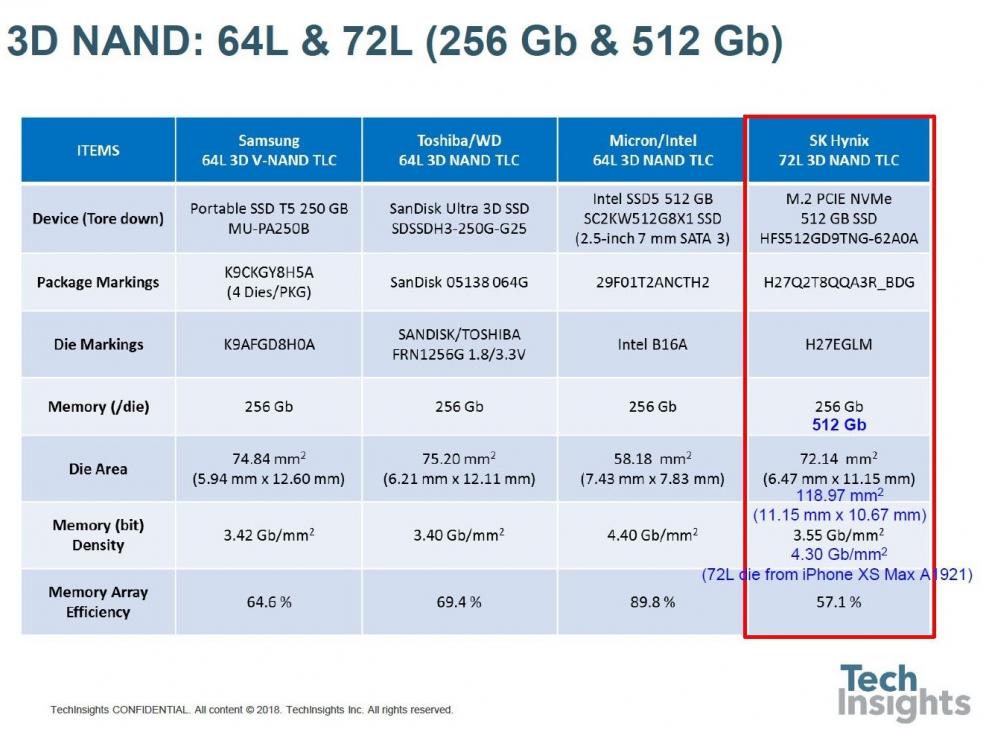

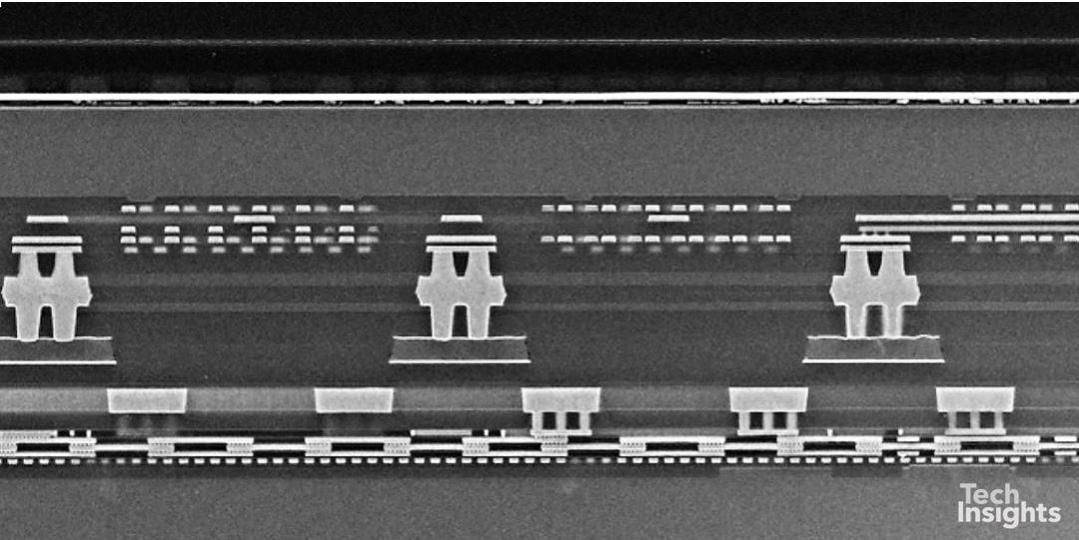

Switching to 3D-NAND, Jeongdong showed us this summary of recent 64- and 72-layer devices:

We can see how the CuA in the Intel part improves the array efficiency to almost 90%, giving the smallest die of the 256-Gb group. The SK Hynix 512-Gb die from the iPhone XS Max has almost the same memory density, an impressive improvement from the 256-Gb part.

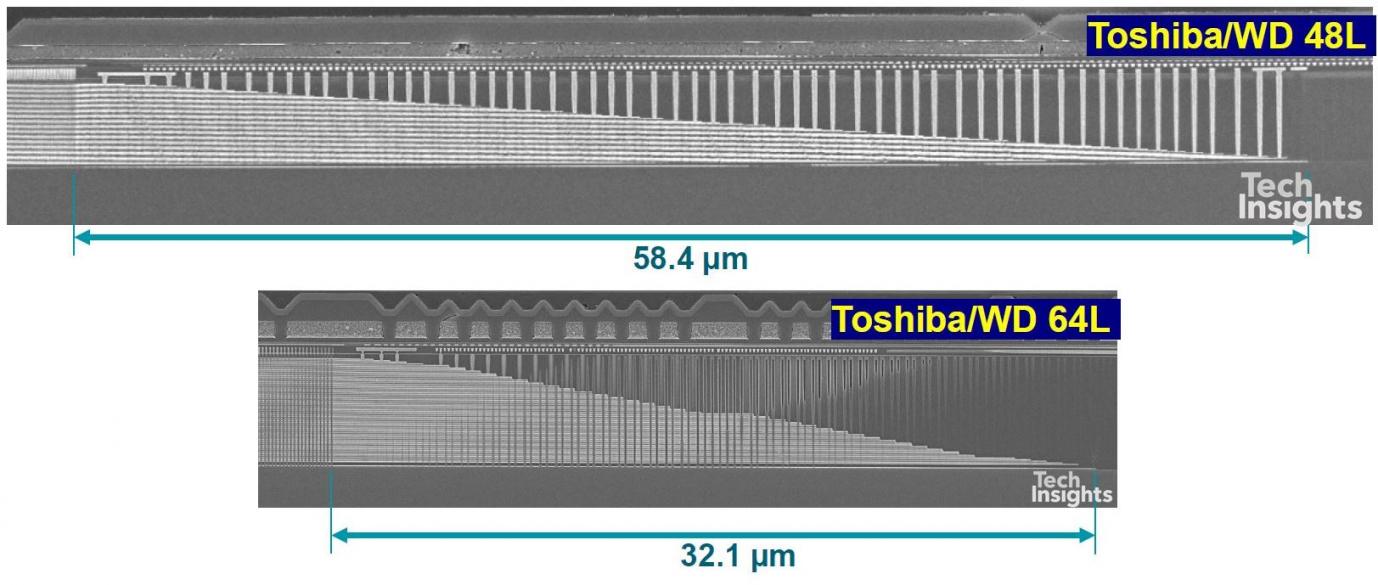

One of the developments made in the transition from 48-layer to 64-layer technology is in the etching of the “staircase” that is used to contact the wordlines in 3D-NAND devices. For example, in the Toshiba/WD parts, the width of the staircase has shrunk by 45% due to etch process improvements and trimming mask changes.

This is not insignificant, even after the shrink the staircase takes up 0.82% of the die area. Similarly, Samsung achieved a 27% width reduction, finishing with a 0.44% area penalty for the staircases.

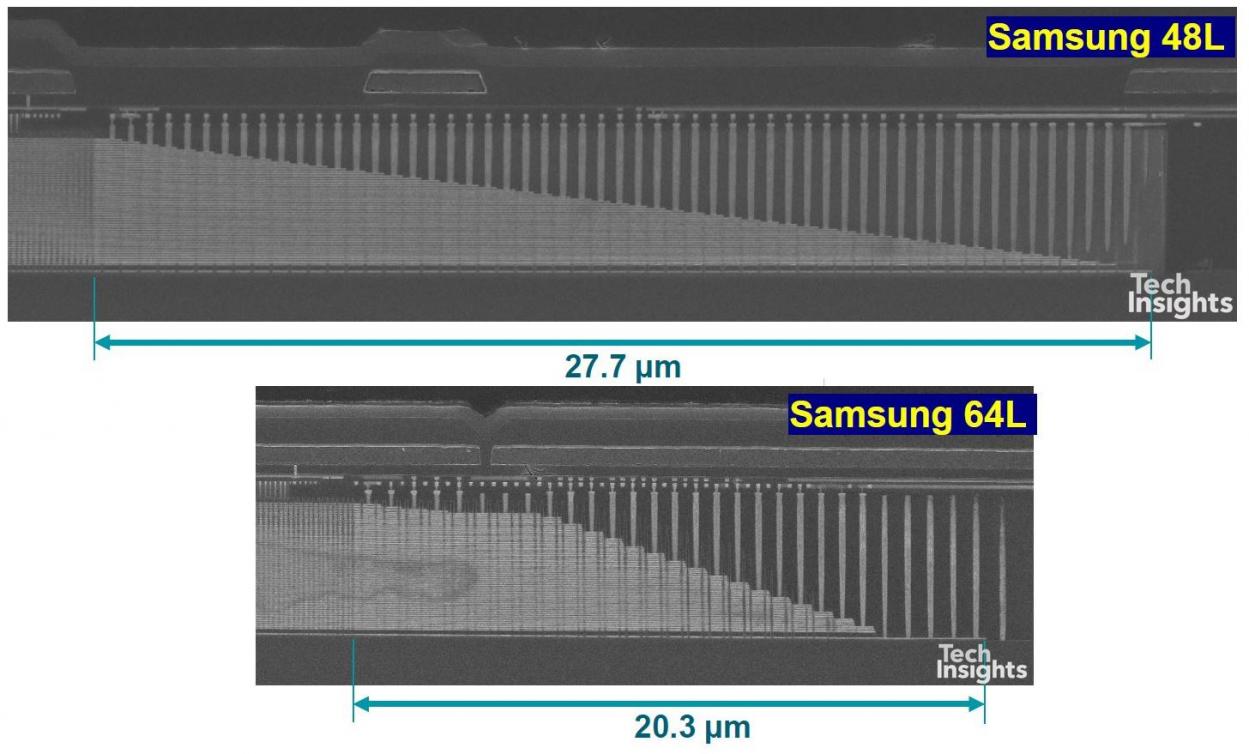

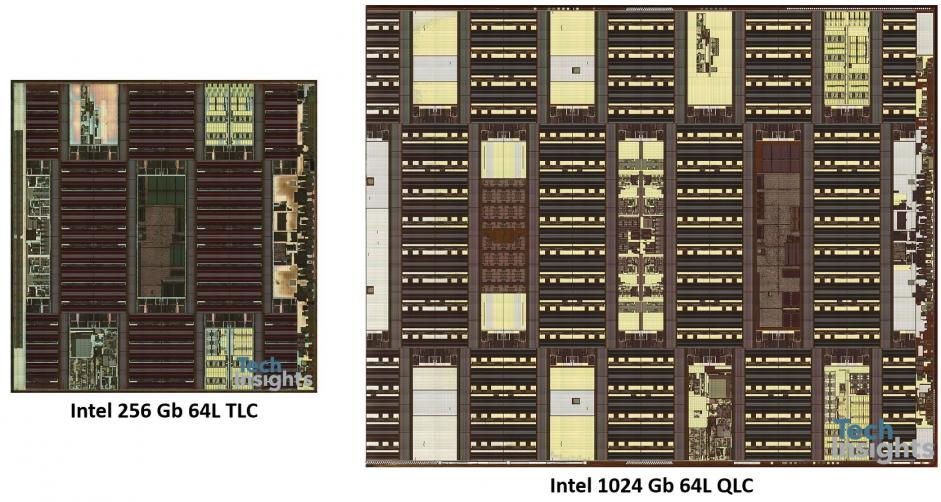

We also had the opportunity to compare Intel/Micron’s tri-level and quad-level cell parts; even though they are both 20-nm, and both 64-level, the bit density goes from 4.4 to 6.5 Gb/mm[SUP]2[/SUP], an increase of almost 50%. We are now in the era of the terabit die, Micron has just announced 1-TB micro-SD cards with eight 1-Tb dies inside!

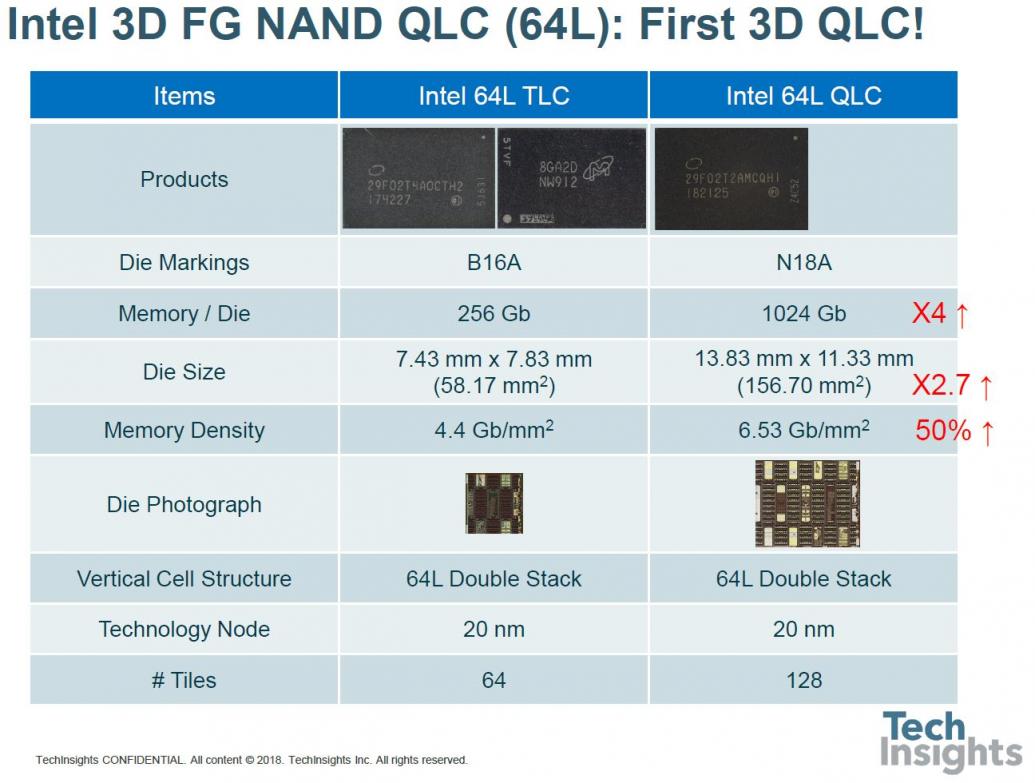

The transistor-level die photos are tiny in the above slide, but they do zoom out quite well:

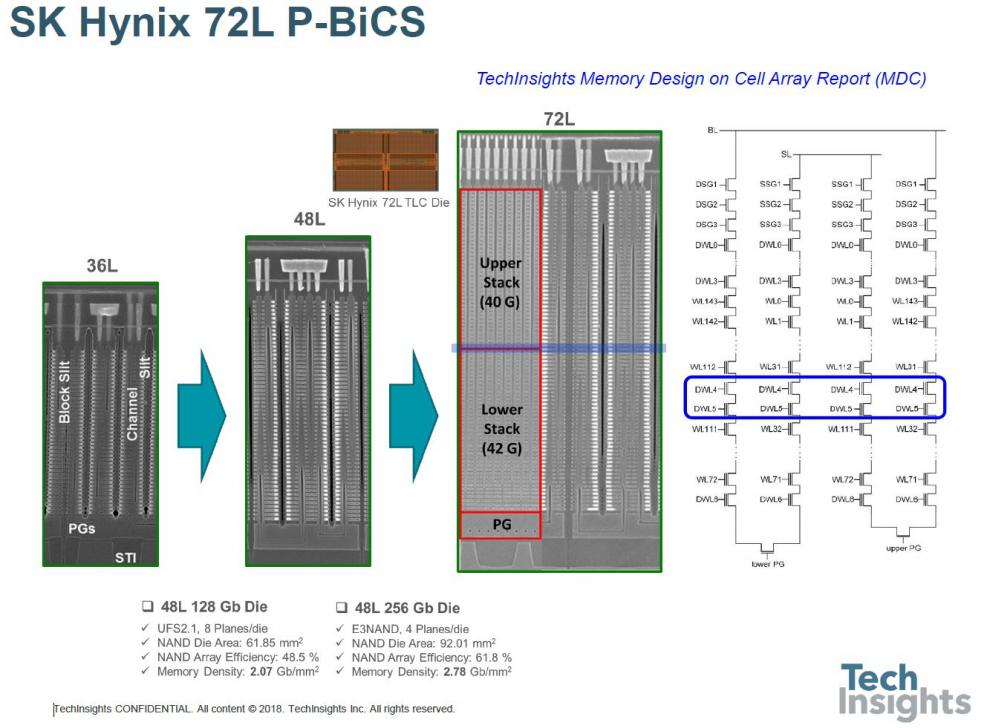

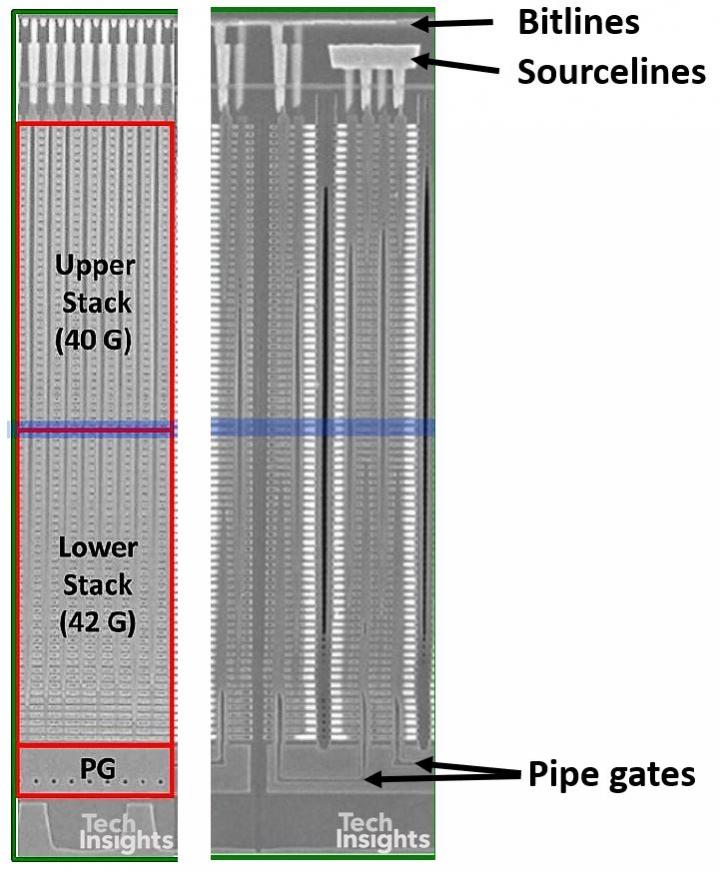

We can clearly see the density of circuitry underneath the array in these shots. Next up was a look at the SK Hynix 3D-NAND, which uses a folded structure.

If we look closely we can see the evolution in the stack from 36 – 48 – 72 layers. The 36L device only has one pass gate, whereas the 48L and 72L have two pass gates, allowing common bitlines and sourcelines for two chains of cells. The centre image of the 72L stack is a little confusing, since it has two orthogonal images glued together – the right side is a section parallel to the bitlines, and the left perpendicular to them. If we look at the separated images, the holes in the PG region show that the left section is through the lower of the two pipe gates, and at the top the individual bitlines are visible.

The upper and lower stacks refer to the two-stage construction of the 82-gate stack. Jeongdong did not go into the details of this in this talk, but he posted a blog on EETimes last June that clarifies that the channel holes are formed with a two-step etching process. The estimated process sequence is:

- Pipe gate mold formation (lower portion)

- Channel etching (lower portion, 42 gates)

- Sacrificial layer filling into holes

- Mold formation (upper portion)

- Channel etching (upper portion, 40 gates)

- Sacrificial layer removal

- Channel formation

The slits and sub-slits are formed by one-step etching of the whole stack. In the circuit schematic above, the blue outline shows the location of two dummy wordlines between the top and bottom stacks, marked by the blue line in the cross-section.

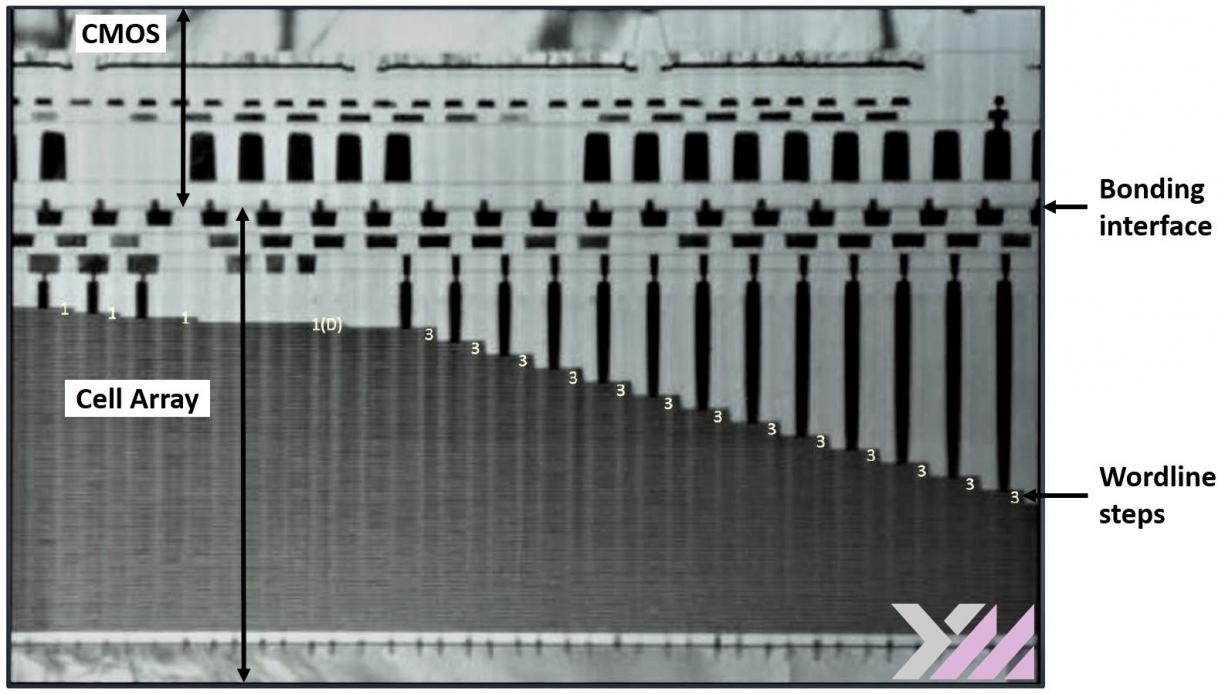

The last NAND device discussed was the YMTC 64L part displayed at the Flash Memory Summit last year. This is their second-generation 3D-NAND technology, using Xtacking to put the peripheral circuitry on top of the memory array instead of underneath it. YMTC uses face-to-face wafer bonding:

I annotated the image that Jeongdong used, to try and clarify what we are looking at:

We have the typical staircase at the edge of the array, and they have helpfully added the number of wordlines per step, showing us that there is one dummy wordline at the top, under the individually-masked select gates.

The wafer bonding gives us a total of seven damascene metal layers, three in the array, and four in the CMOS, and in the cell stack there are a total of 74 tungsten wordlines. It’s not specifically mentioned in any of YMTC’s pronouncements, but historically they have worked closely with Spansion (now Cypress) using charge-trap storage in NOR flash, so it seems likely that their 3D-NAND is also charge-trap based.

The bonding is likely the DBI® (Direct Bond Interconnect) technology from Xperi – it’s quite a fuzzy TEM image above, but it does look similar to the interface in this SEM cross-section of the Sony IMX260 stacked image sensor (below), which we know uses the process.

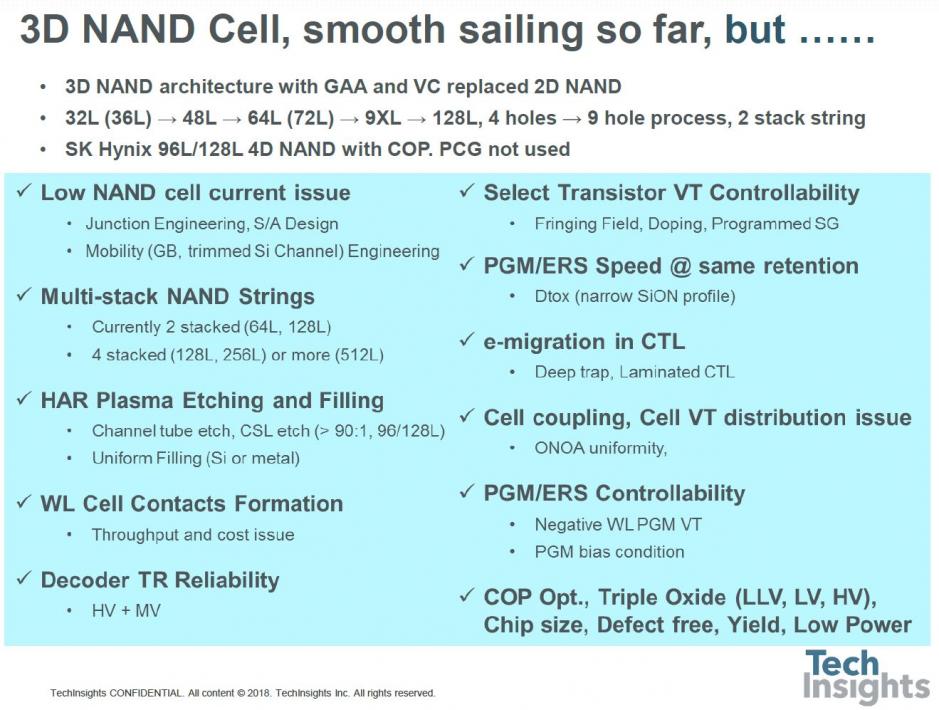

Jeongdong finished up the NAND flash section with a couple of summary slides, the first describing the innovations in 3D NAND so far. It’s a busy slide, so I won’t go through it in detail – there is a lot of innovation! Aside from the 3D stack itself, there are possibly unexpected features such as the epitaxial (SEG) transistors (Samsung), CuA and double-string stacks (Micron), and pipe gates (SK Hynix). And now we have wafer bonding!

The summary slide tracked the progress so far, and raised some of the concerns for future development:

Of note to me are SK Hynix’ return to a conventional stack without the pipe gates, Micron’s (presumably) to four-stacked strings, and the generic problems of etching and filling very high aspect ratio channels.

This is turning out to be a long article, so I will cover the DRAM and Emerging Memories segment of the talk in Part 2, coming up.

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center