The recent Chiplet Summit at the Santa Clara Convention Center was buzzing with many enabling technologies for chiplet-based design. Collaboration was also on display during many parts of the show. A presentation in the Siemens booth was a perfect example of both of those trends. In the Siemens booth, Perforce presented an excellent overview on how to enable 3DIC design. In case you missed it, here is a summary of how Perforce and Siemens collaborate on 3DIC design at the Chiplet Summit.

The Collaboration

There is a history of collaboration between these two companies. Some details of the work was disclosed in a press release last May. The presentation at the Siemens booth was given by Vishal Moondhra, VP of Solutions at Perforce. Vishal is the primary driver for this work for Perforce. Michael Munsey, VP Semiconductor Industry at Siemens Digital Industries Software drives the program from the Siemens side. These gentlemen have spoken about collaboration between the two companies before. You can read about the details of what they said at last year’s DAC on SemiWiki here.

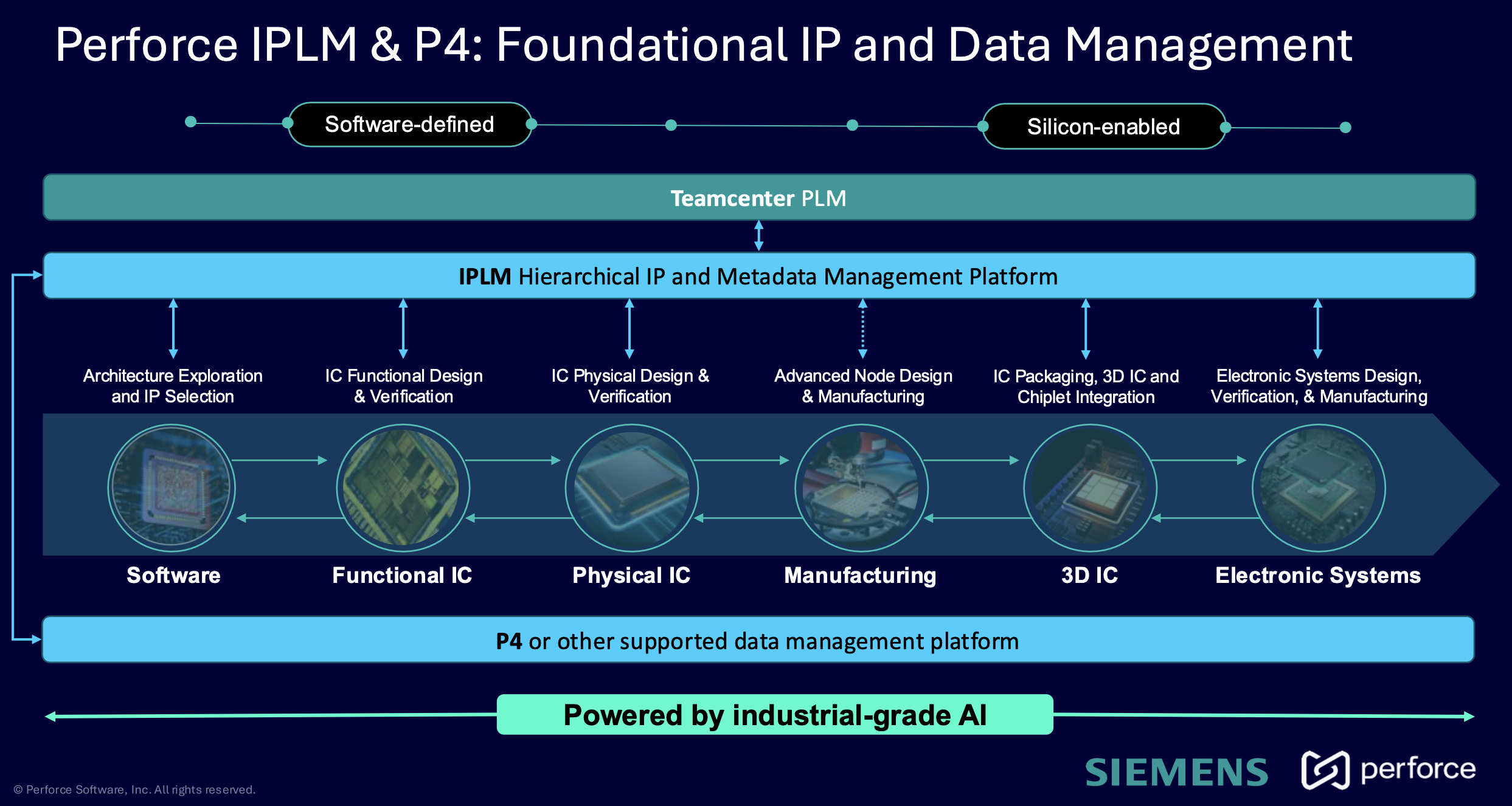

The Perforce/Siemens collaboration is both ambitious and extensive. The work reflects a shared vision of both companies. This vision includes the fact that we are moving to an environment where product innovation is software-defined, AI-powered, and silicon-enabled. As product development shifts to prioritize software and silicon at its core, Perforce and Siemens are working to deliver the unified development platforms needed to empower the next generation of product engineering.

The Presentation at the Siemens Booth

The presentation began with a discussion of IP and data management challenges in 3DIC design. The issues and risks here include:

- Fragmented data and siloed teams across the silicon, package, and system domains resulting in version mismatches, manual handoffs, and delayed design iterations.

- Poor visibility into where IP is used, which versions are valid, and the impact of changes which can cause unintended design divergence and late-stage issues.

- Lack of end-to-end traceability and data provenance which leads to higher risks for design escapes, audit gaps, and costly respins.

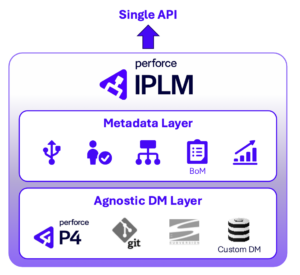

Two key products from Perforce were then discussed. These products enable scalable, audit-ready IP management while providing the foundation for integrating Siemens EDA solutions with traceability and cataloguing workflows. The products discussed were:

Perforce IPLM, an IP lifecycle management platform that provides traceability, cataloging, and metadata insights across design assets. This includes dependencies, permissions, hierarchy, properties, and usage at the IP and block levels.

Perforce P4, which delivers an enterprise-grade version control system for hardware and software co-design. The tool manages and delivers software, firmware, and hardware design file information.

The benefits of unified metadata and how it delivers cross-domain visibility were then discussed. Key points here include the fact that all silicon, chiplet, package, and system metadata are managed in a single system for a complete view of the project, including all versions and dependencies.

This improves visibility and alignment across electrical, physical, package, and system design domains. Blind handoffs and conflicting design assumptions are eliminated thus reducing rework. Overall, this approach enables faster, better-informed decisions across globally distributed 3DIC programs. Some more details are provided in the graphic on the right.

This improves visibility and alignment across electrical, physical, package, and system design domains. Blind handoffs and conflicting design assumptions are eliminated thus reducing rework. Overall, this approach enables faster, better-informed decisions across globally distributed 3DIC programs. Some more details are provided in the graphic on the right.

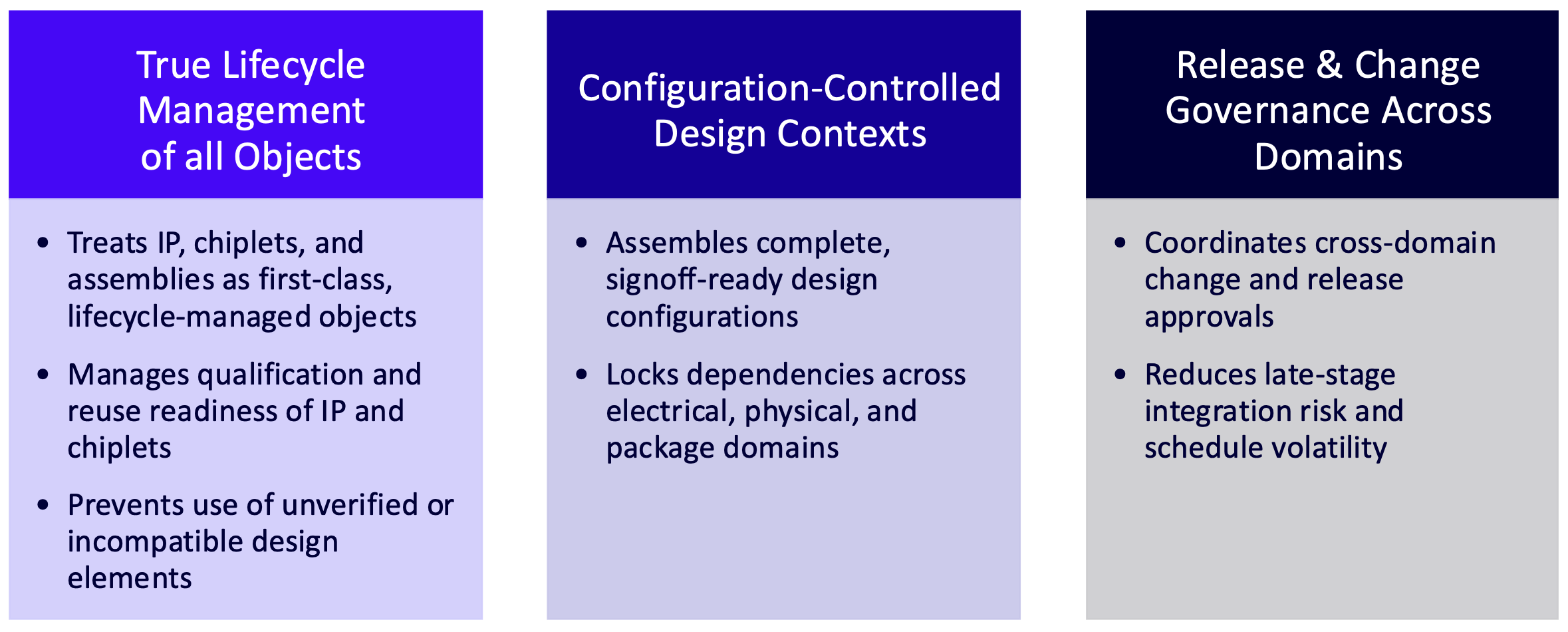

The impact of a unified, hierarchical 3DIC bill of materials (BoM) was then explored. It was pointed out that everything is an IP, from blocks and chiplets to software and complete platforms. IP can now be managed consistently from the block-level through die, package, and system assemblies in a single lifecycle framework. The full chiplet-to-system structure is now captured in a versioned, immutable hierarchy.

Traceability, data provenance, and dependency tracking can now be enforced across domains. And IP version conflicts can be detected to enforce compatibility rules across chiplets and assemblies to reduce integration risk.

All this work delivers easier IP reuse with configuration-controlled releases. The graphic below was used to summarize some of these benefits.

The Backstory

I had the opportunity to speak with Vishal after his presentation. He provided some perspective on how this work is changing today’s design flow and what impact it can have on the future. We began with a discussion of the siloed behavior that exists currently in many design organizations. Each phase of the design is handled by different teams with expert skills and highly tuned tools. It isn’t surprising that this singular, task-oriented focus can create silos of activity.

Vishal explained that massive metadata is accumulated at each phase of the design. Perforce aims to integrate all that metadata and deliver a unified view across all design teams. The availability of an integrated view will begin to break down some of that siloed behavior by providing a broader and valuable view of the design process.

Vishal described future work that holds promise in another direction – an intelligent, process-oriented view of the design flow. That is, having insight into what happened before the current step and what will happen after the current step can facilitate a more intelligent workflow. An example he provided was power optimization, which occurs throughout the design process. At any given step, there is an optimal amount of power optimization to deliver based on what has happened before and what will happen after. Too little optimization will make future steps more difficult, but too much optimization can be wasted effort for future steps that take a broader view of the problem.

The current focus is on comprehensive integration of tools and metadata. The next phase will use that integration to deliver a more intelligent flow. In Vishal’s words, “integration first, intelligence next.”

The presentation concluded with a broad overview of how Perforce is working with Siemens to enable 3DIC design across the entire flow. The graphic below shows the substantial breadth of the solution.

To Learn More

I have just touched on the work Perforce and Siemens are doing. Here are some links to help you dig deeper. Perforce IPLM, Perforce P4, and more details on Perforce/Siemens collaboration.

If 3DIC design is in your future, this information will be quite valuable. And that’s how Perforce and Siemens collaborate on 3DIC design at the Chiplet Summit.

Also Read:

2026 Outlook with Kamal Khan of Perforce

What’s New with IP Lifecycle Management (IPLM)

5 Lessons the Semiconductor Industry Can Learn from Gaming

Share this post via:

Comments

One Reply to “Perforce and Siemens Collaborate on 3DIC Design at the Chiplet Summit”

You must register or log in to view/post comments.