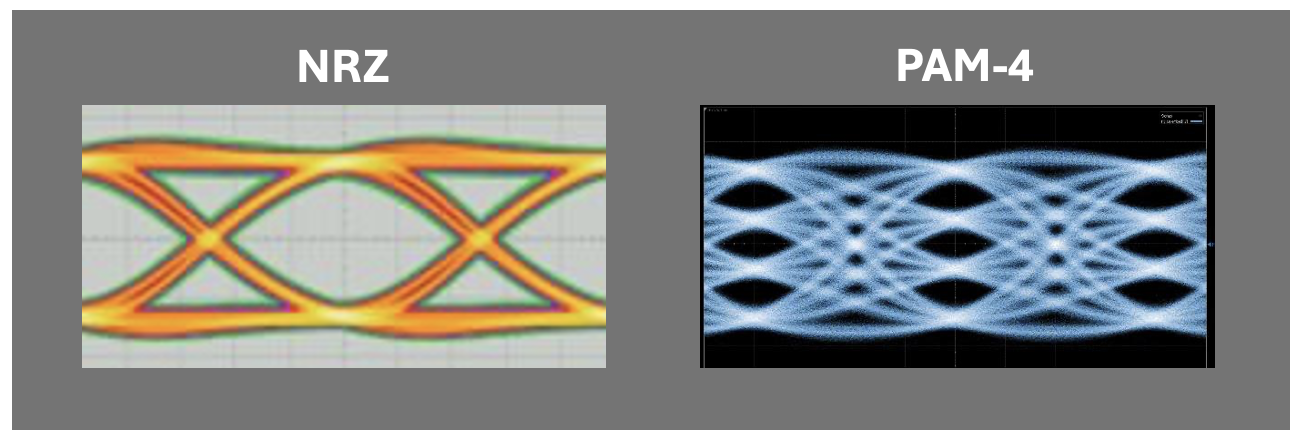

Data communication speeds continue to grow. New encoding schemes, such as PAM-4 are helping achieve faster throughput. Compared to the traditional NRZ scheme, PAM4 can send twice the signal by using four levels vs. the two used in NRZ. The diagram at the top of this post shows the how data density is increased. With progress comes challenges. PAM4 has a worse signal-to-noise ratio, and reflections are also much worse. More expensive equipment is required and even then, there are challenges in establishing a link. There were a couple high-profile events recently that showcase what Synopsys is doing to address these challenges. Capabilities of its IP were demonstrated, as well as how a reference design from Synopsys is helping with interoperability across the ecosystem. Let’s take a closer look to see how Synopsys is paving the way for success with 112G SerDes and beyond.

Webinar Presentation

On February 20 a webinar was held to explore how to get the best performance out of a 112G SerDes solution. The challenges of PAM-4 were discussed, along with the the importance of auto negotiation (AN) and link training (LT) to address those challenges. Three knowledgeable people participated in this webinar, as shown below.

Madhumita Sanyal from Synopsys began the webinar with a presentation. She discussed the growing use of high-speed ethernet in many applications and how 112G ethernet is enabling 400G and 800G. On this topic, she discussed the role of PAM-4 modulation as an enabler and some of the design challenges PAM-4 presents.

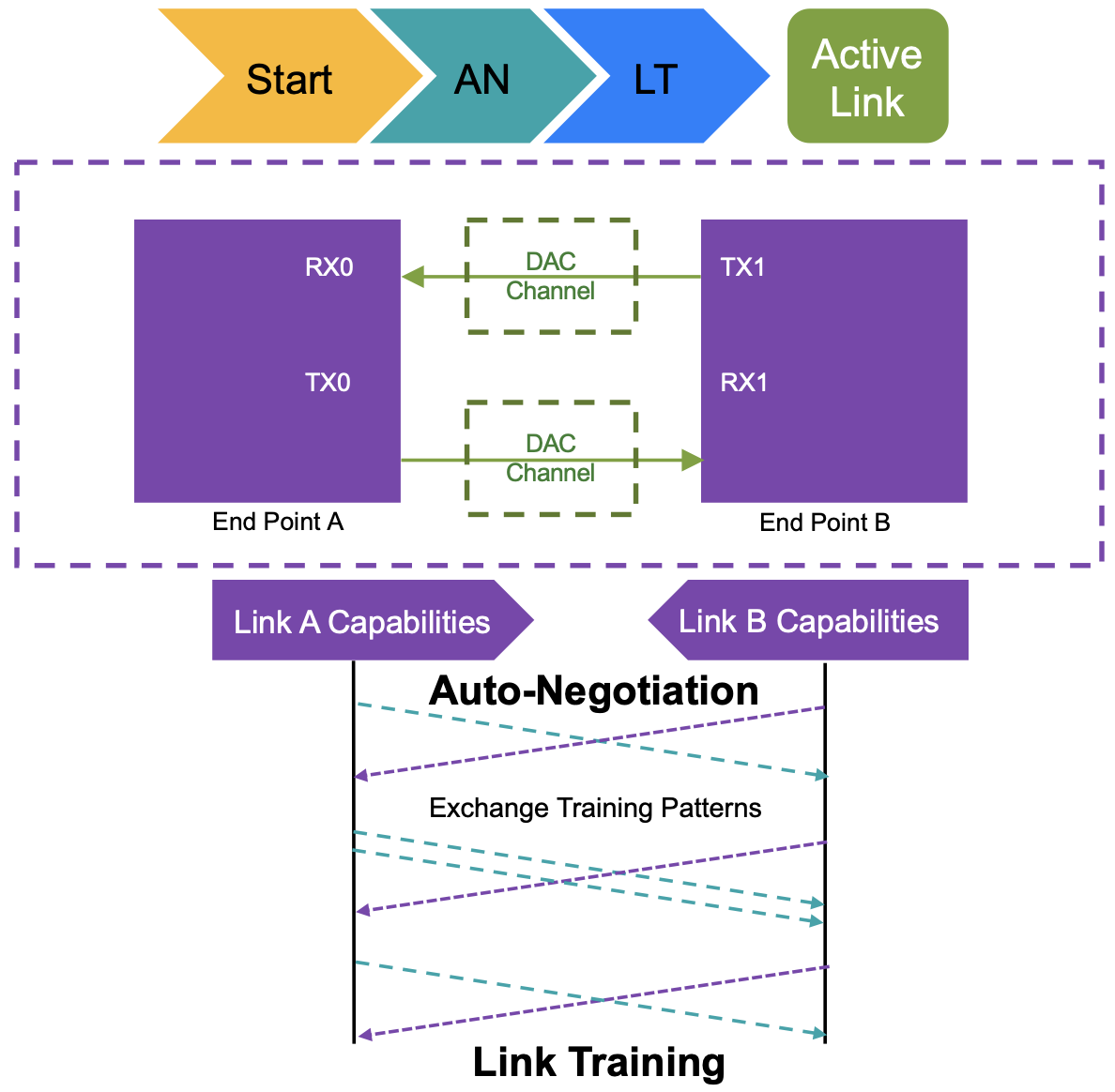

Madhumita went on to discuss the importance of auto-negotiation and link training to help address the challenges presented by PAM-4. She cited several design examples. The approach is applicable to copper cables and backplanes. She explained that PAM4 challenges are partly compensated through a Tx equalization after auto-negotiation is completed. She also pointed out these techniques are applicable to all rates defined in IEEE 802.3 Clause 73 (ranging from 1G to 200G) and the Ethernet Consortium 400GBASE-CR8/KR8 specification. The figure below summarizes the discussion.

The Webinar also presented a very useful interoperability demo. I’ll get to that in a moment, but first some other news from the trade show floor is quite relevant.

News From the Trade Show Floor

At the 49th European Conference on Optical Communications (ECOC) last October, Madhumita Sanyal presented impressive details of the impact the Synopsys 800G ethernet subsystem link-level interoperability was having across the ecosystem.

The 800G demos at ECOC’23 were done in the Ethernet Alliance booth. The demos used 8 lanes of Synopsys LR 112G ethernet PHY IP and 800G MAC/PCS interop with exercisers, analyzers & third-party 800G EVBs over DAC channels showing linkup, packet receive/transfer, FEC histogram & other performance metrics.

800G ethernet throughput was shown with zero errors across several demonstrations integrating Synopsys products with ecosystem partners. This interoperability success highlights the possibilities for future design collaboration across the ecosystem. The figure below illustrates one HPC data center rack-like demo configuration.

You can view a complete summary of this work from the show floor at ECOC with this short video.

The Webinar Demo

A detailed demonstration of interoperability based on the Synopsys 800G SS evaluation board was featured during the recent webinar as well.

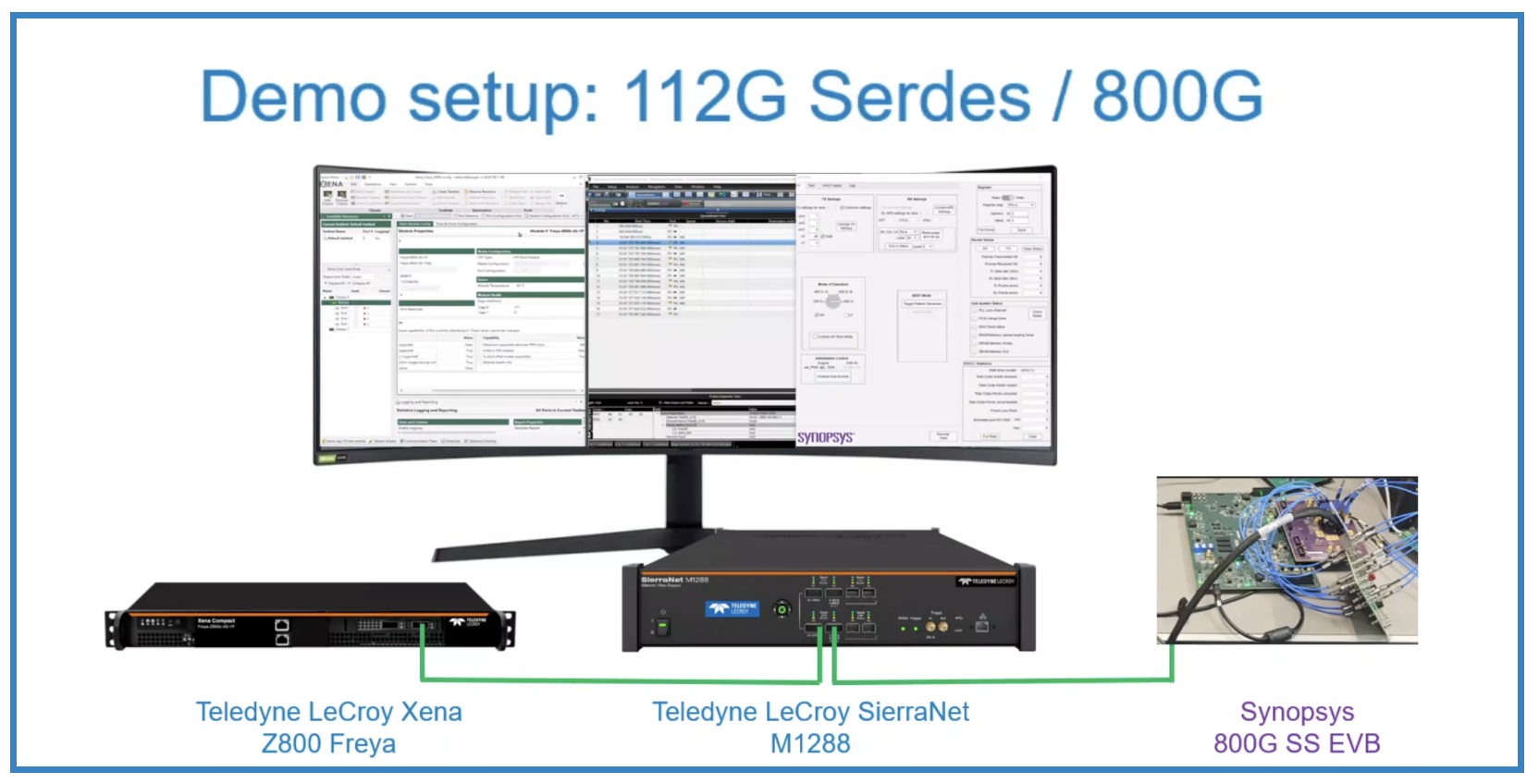

Martin Qvist Olsen of Teledyne LeCroy set up the first demonstration. The demo configuration is summarized below. A Teledyne LeCroy Xena Z800 Freya tester connected to a Synopsys 800G SS evaluation board with a Teladyne LeCroy SierraNet M1288 in between as a probe.

The first demo showed how the Xena and Synopsys devices performed auto-negotiation. Details of the operation of each device was shown by examining UI outputs to explain how the results were achieved. The protocols and standards used were also discussed, along with the details of tuning and the associated challenges.

Martin then moved to the next demonstration, which focused on how the Xena and Synopsys devices initiate automatic link training and how the devices perform the link training. The ways the performance of the link is improved was also covered. Details of FEC and BER statistics were shown. The impact of standards and what is covered by those standards was also discussed.

The third demonstration was also presented by Martin. Here, the detailed steps of how link training is achieved are examined. The steps involved and the associated pre-sets were shown. A great amount of detail of how the process works and how optimal results can be achieved were reviewed with many examples.

The next demonstration was presented by Craig Foster of Teledyne LeCroy. Craig focused on the various ways to implement link training. How the Xena device performs link training on its own is examined. This is followed by how the Synopsys device implements link training on its own. And finally, how the two devices work together to implement link training was reviewed.

Craig covers a lot of detail regarding how each device implements link training and then how they work together. The attendees were able to view, step by step, how each device works.

Martin presented the final demonstration, which is the Xena and Synopsys device running a 1X800G channel. The parameters used to implement the link are shown in detail, along with performance statistics.

To Learn More

This masterclass webinar is rich in technical information, backed up with practical demonstrations to show the details. If high-speed communications is important to you, I highly recommend you take a look. You can access the webinar replay here.

Also, as mentioned, you can view a summary of the Synopsys interoperability work from the show floor at ECOC here. Synopsys provides a complete Ethernet IP solution for up to 1.6Tbps, including MAC, PCS, PHY, VIP and security.

And that’s how Synopsys is paving the way for success with 112G SerDes and beyond.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.