Edmond Macaluso, President of Z-Circuit Automation met with me at DAC on Tuesday afternoon to provide an overview of how their EDA tools characterize cell libraries.

What’s New?

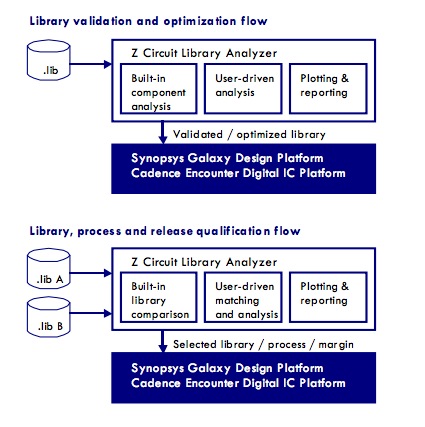

Enhanced our validation flow to crosscheck all the views produce by our characterization tools, to make sure they are consistant with SPICE netlist.

Customers?

Large semiconductor companies on low-power models, multi-voltage, power gating techniques.

Number of customers in general: 10-20 customers in US and Taiwan (Maojet is distributor in Taiwan). ROth and Yelnik are distributors in US.

Evaluation of tools: weeks to months of time.

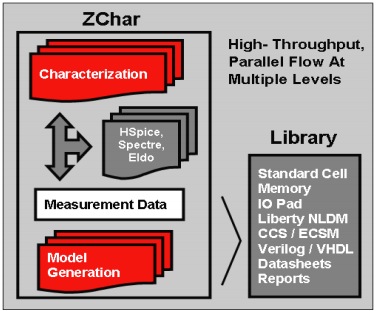

Char – std cells, IO pad and Memory char with one tool. Fast. Accurate. Complex cell characterization, specialty cells, low power modeling.

WOrks with any SPICE simulator, even Fast SPICE simulators.

Primary competitors: Cadence, Synopsys, Magma (SiliconSmart).

3rd party programs: Synopsys inSync, HSPICE Integrator. Mentor OpenDoor. Cadence Connections.

20nm challenges – low power is more difficult, more voltage maps and voltage domains.

How do you characterize for reliability effects?

Aging effects will be added.

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center