The Automotive IC market is not the largest segment, but is certainly the segments expected to grow with the highest CAGR, with 10.8% from 2013 to 2018, according with IC Insights (January 2015). If you consider the pretty long concept/design to production cycle time (7 years or more) as well as the numerous segments just emerging in production, like Infotainment, Vehicle Networks, Driver Information and Driver Assistance, you can predict that Automotive IC market growth will stay in the double digits up to 2025… and probably further, when the various innovations integrating high semiconductor value will generate additional IC production.

The sky will be blue in the future for chip makers and IP vendors targeting automotive… at the condition to meet certain quality requirements unique to automotive and very stringent. A device supporting automotive infotainment may exhibit the same features set than a similar IC integrated into consumer system, but the way to design it, the various IP (including the foundation IP) integrated in it, the fault simulation rate target, the test and even the way to manufacture the IC will be different, more stringent and demanding.

Automotive Grade requirements for IP are multiples, and well documented. To reduce risk and accelerate qualification for automotive SoCs, Synopsys’s foundation IP, as well as the more complexes IP, must comply with these functional safety, reliability and quality requirements:

- Functional Safety

- Automotive Safety Integrity Level (ASIL) A/B/C/D defining the level of safety required

- ISO 26262 functional safety assessments defines the processes and standards to meet to help ensure designers reach ASIL levels

- Reliability

- AEC-Q100 qualification of SoCs

- Quality

- TS 16949 Quality Management

These various standards have been defined to minimize the susceptibility to random hardware failures, and the “good design practices” implies to follow certain rules in the development process: defining the functional requirements, applying rigor to the development process, taking necessary design measures and finally applying systematic analysis methods. The Compliance certifications for SoCs is granted by accredited providers, Synopsys is working closely with SGS-TUV to speeds SoC safety assessment and certifications.

As of now, that we have described is rather theoretical, but when we take a look at the various IP specifically developed or redesigned by Synopsys to address the automotive market, we realize that the investment is at the level of the market size expectation, pretty high!

Synopsys’ “safety culture” implements policies, processes, strategies & safety managers supporting safety-related IP development. Functional safety is linked with ISO 26262 and the various related documentation:

- Integrated hardware safety features

- Verification plan

- Failure mode effect and diagnostic analysis (FMEDA) assessment

IP level functional safety compliance or documentation can be used as input to the chip-level, like for example (IP level) Fault-Mode Report can be used for the (chip level) FMEDA report.

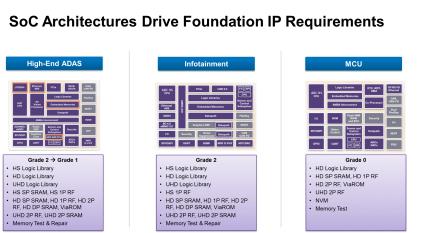

How Designing Grade-Appropriate Foundation IP and what are the Grade 2, Grade 1 and Grade 0 different reliability levels requirements?

Grade 2 is the basic level, with reliability requirements similar to consumer electronics, except that functionality should be validated up to 125°C junction temperatures.

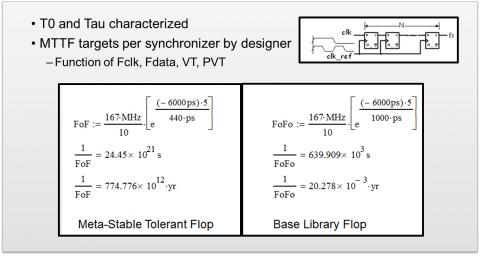

With Grade 1, the requirements begin to be more stringent: the functionality should be validated up to 150°C junction temperatures, the reliability requirements (<1 DPPM) becomes more stringent with electromigration (EM) profiles becoming application specific and memories integrating ECC. The function should support advanced ESD rules with clamps, the meta-stability (T0, Tau) has to be improved and logic libraries should be fault tolerance.

The above picture describe how to implement Flip-Flop for crossing clock domains for grade 2 compliance (adding DFF) and the results obtained when using Meta-Stable tolerant DFF (one error every 774 10[SUP]12[/SUP] year!), to be compared with base library DFF, where an error may occur every 20 10[SUP]-3[/SUP]year or every 7 days!

Grade 0 is the most stringent the functionality should be validated up to 175-200°C junction temperatures, the reliability requirements (<0.1 DPPM) becomes very stringent with electromigration (EM) profiles becoming application specific, memories integrating ECC and the need to double vias/contacts and increase tap frequencies. The other requirements are staying the same as for Grade 1.

The AEC-Q100 industry standard specification outlines the stress tests and reference test conditions for the qualification of automotive grade SoCs. Synopsys is investing in providing IP that meets AEC-Q100 requirements, enabling designers to reduce design risk and development time for SoC level AEC-Q100 qualification. The specific test are ranging from fault simulation, accelerated lifetime simulation test, die fabrication reliability test to ESD, latch-up and characterization impacting IP (or Foundry) quality when accelerated environment stress test, EMC, SC and soft error rate (SER) are applying to the SoC only.

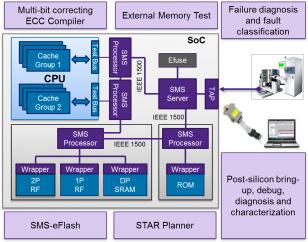

If we take as an example of foundation IP Synopsys STAR memory system, claimed to be the Best-in-Test Memory Test, Repair and Diagnostics, STAR has been greatly improved to support automotive SoC design. STAR has been enhanced to cover FinFET-specific faults, with new techniques for memory repair, still offering Power On Self Test (POST) and in system testing support. Moreover the product is ASIL D ready for ISO 26262 certification. Just take a look at STAR implementation on the above picture: STAR is much, much more than a memory compiler! Last point, Synopsys has released industry’s first commercial BIST solution for Embedded Flash, also available for eFlash IP from the competition.

All Automotive SoC have to comply with Functional Safety, Reliability and Quality standard and Synopsys is offering an IP port-folio to automotive design team that allows shortening qualification effort and reduce Time-To-Market… remember that these emerging automotive applications like ADAS or Infotainment are mixing avionics like requirements with consumer like TTM!

You will find an exhaustive list of Synopsys Automotive Grade IP in this Brochure

From Eric Esteve from IPnest

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.