Hybrid IP Prototyping Kit from Synopsys!

Synopsys has launched IP Accelerated initiative last year. The goal was clearly to accelerate Time-To-Market by providing a complete set of “tools” to augment design productivity:

- IP Prototyping Kit with reference designs work out-of-the-box

- IP software development kits enable early SW bring-up, debug and test

- IP subsystems (customized integration and testing of Controller and PHY IP) to lower risk and speed time to market

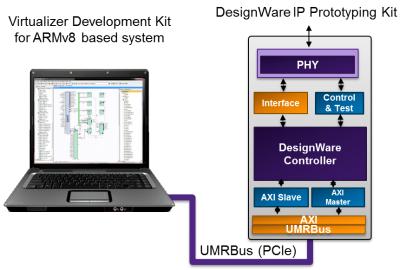

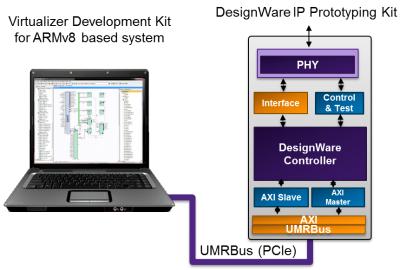

How to further boost system-on-chip design integration? When the SoC integrates one of the high performance ARM Cortex A57 or A53 64-bit processor IP core, the customer want to test the real world interface with this 64-bit system, on top of developing around the DesignWare IP (thanks to IP Accelerated). Adding a Virtualizer Development Kit (VDK) for ARMv8 based system to the DesignWare IP Prototyping Kit will create this Hybrid IP Prototyping Kit:

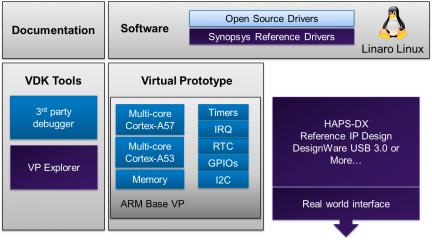

If we take the example of a design team developing an ARMv8 based server chip, boosting software developer productivity will accelerate TTM. Using Virtual Prototype for ARM Cortex A57 (A53) is a known good solution for develop software faster, and even more in a multi-core environment. Hybrid IP will enable connecting the software development kit with HAPS-based DesignWare IP prototyping kit. In the above example of USB 3.0 IP subsystem (PHY + Controller) integrated in the SoC, the design team can fix S/W issue by going back to the virtualizer or benefit of a fast iteration flow for easy modification of the USB 3.0 IP. Synopsys call this tool-set “Hybrid IP”, as the designer can optimize software change and hardware modification by using a unique flow and using UMRBus to join Virtual and Physical worlds.

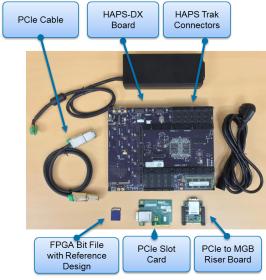

The physical world is a close as possible with the target SoC and is represented by the well-known HAPS-DX based IP development kit, comprising the out-of-the-box reference design (controller + PHY + system logic) and allowing:

- Pre-optimized, pre-loaded Linux OS & reference driver

- Fast iteration flow for easy modification of IP

The IP integrated into HAPS-DX board is a proven target for early software development. Thanks to the PCIe based UMRBus, on a x4 PCIe gen-2 interface which is offering 20 Gbit/s bandwidth, the designer can connect immediately (and fast) with the Virtualizer Development Kit to access the multi-core processor virtual model, including the memory and peripherals:

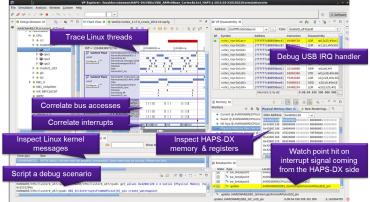

Hybrid IP Prototyping Kit provides a very intuitive way to run hardware and software debug at the same time with a high confidence degree as the Interface IP (USB 3.0 in this case and PCI Express, MIPI UFS and DDRn to come soon after) is the exact configuration of the controller and PHY to be integrated into the design and ARMv8 virtual prototype is the best available model that a designer can use to speed up hardware and software co-development. Using Hybrid Prototyping will not only speed-up TTM, it will allow optimizing the system solution as the designer can intuitively play and modify the hardware at the same time that modifying the software, as all the tools can be integrated together within the same user interface, as we see below:

The benefits are multiple: Hybrid IP Prototyping Kit allows fast IP bring-up and debug with complete reference design of VDK and Interface IP together. The reference design includes fast iteration flow with easily modified Interface IP design/build scripts. The designer can explore system drivers with real-world I/O and 64 bit processors. The reference drivers & application provide early software bring-up, debug and test with support for Linux. Last but not least, Hybrid IP Prototyping Kit is expandable and scalable to SoC prototypes.

From Eric Esteve from IPNEST

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.