When I hear the phrase Static Timing Analysis (STA) the first EDA tool that comes to mind is PrimeTimefrom Synopsys, and this type of tool is essential to reaching timing closure for digital designs by identifying paths that are limiting chip performance. Sunil Walia, PrimeTime ADV marketing lead spoke with me by phone on Thursday to provide an update. The base STA tool from Synopsys is called PrimeTime SI and it provides:

- Timing delay and noise analysis

- ECO (Engineering Change Orders) guidance

- Hierarchical analysis

An upgrade to PrimeTime SI is called PrimeTime ADV and it adds features like:

- Advanced ECO

- Parametric On-Chip Variation (POCV)

We first started hearing about PrimeTime ADV last year, and since the product introduction there are about 90 customers with 75 tape outs using this, so adoption is growing.

Related – Is Number of Signoff Corners an Issue?

ECOs

ECOs were historically implemented with a manual or scripted approach, however in the lat Last 5-6 years smaller process nodes have meant many more IP blocks, smaller routing channels and even tighter spaces to make changes in. Automating ECOs is more important now, not just for meeting timing, but also for power because of the interdependencies. About 3-4 years ago new patented ECO technology was developed within Synopsys to meet these new challenges.

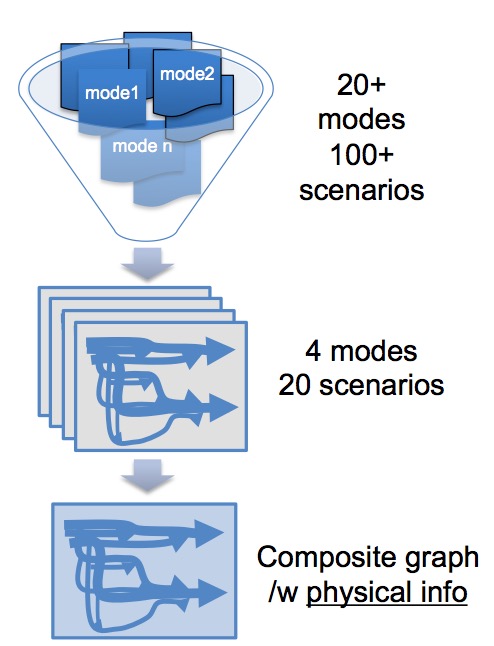

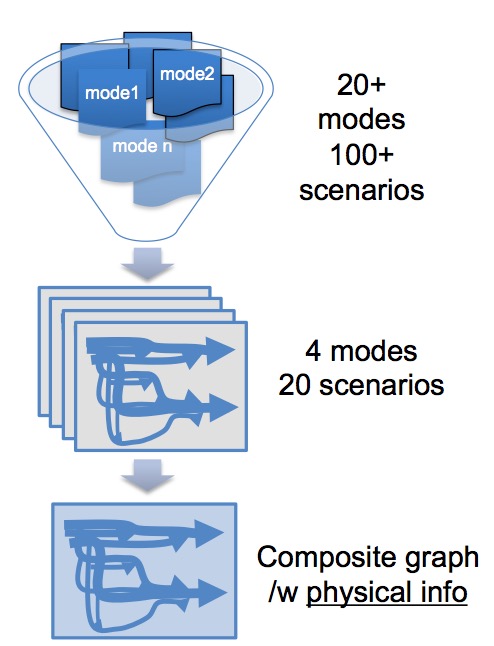

One STA approach for ECO guidance looks at each end point in a timing graph, finds timing violations in the path, and then sizes the cells or inserts buffers to meet timing. This does work automatically, but it increases die size area and is not too scalable. With PrimeTime ADV the approach to ECO guidance is to collapse all endpoints into a global graph, and find an optimal location to fix the most violations – not just one violation. Fixes should not break anything. The composite graph takes into account all scenarios: more scalable, memory efficient, faster run times.

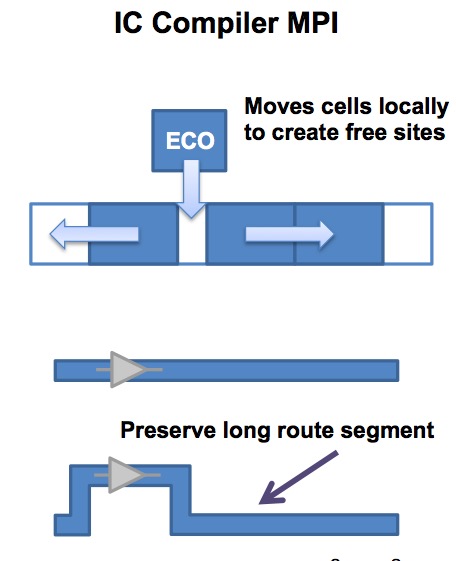

Another improvement with PrimeTime ADV is that physical dimensions are added to constraints now, so it knows the P&R congestion – what is open for buffer insertion and blockages. PrimeTime ADV reads in LEF and DEF physical data, then tells the Place & Route tool – IC Compiler where to make the changes with a Minimum Physical Impact (MPI):

You can still use PrimeTime ADV with other P&R systems: Cadence, Mentor, Atoptech. The IC Compiler MPI is unique to the Synopsys methodology.

Related – Enabling 14 nm FinFET Design

On-Route Buffering

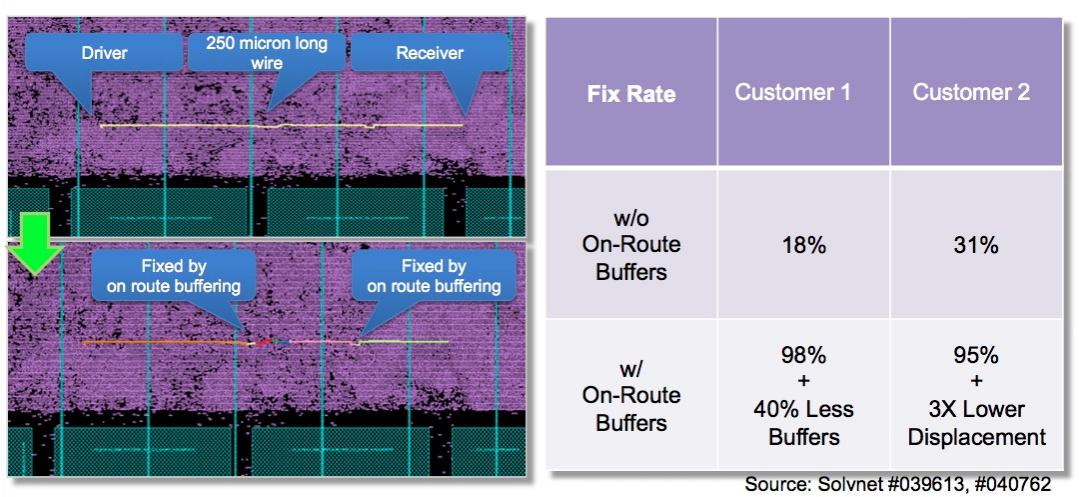

Another new feature is called on-route buffering where it is adding buffers along the route, knowing where there are physical openings, spread out along the net, even estimating the interconnect parasitics to make the split net optimal.

In the mobile market designers value power reduction techniques. Because PrimeTime ADV has knowledge of sign-off timing, it can find positive slack and then optimize to further reduce leakage power by 10-15% through swapping cells with a higher Vt value, and this approach is quite easy to use.

Another power-reduction technique is down-sizing of cells, helpful to reduce dynamic power. PrimeTime ADV can do both down-sizing and Vt swapping together.

Hierarchy

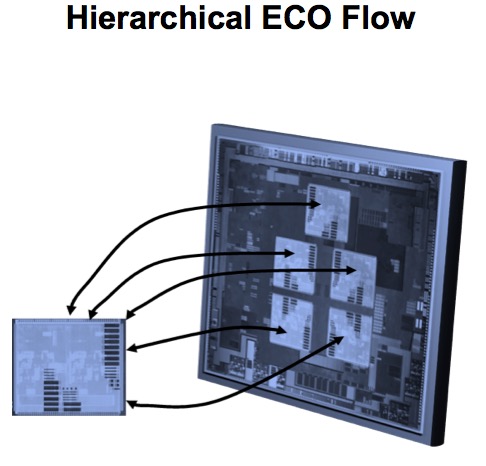

Hierarchical ECO guidance is a technique that supports multiply-instantiated modules (MIM), so consider an SoC with 5 identical cores. During timing analysis the graph is flattened to get precise timing, and with MIM it can satisfy all of the timing requirements for each of the repeated cores in a single analysis run.

Variation Technology

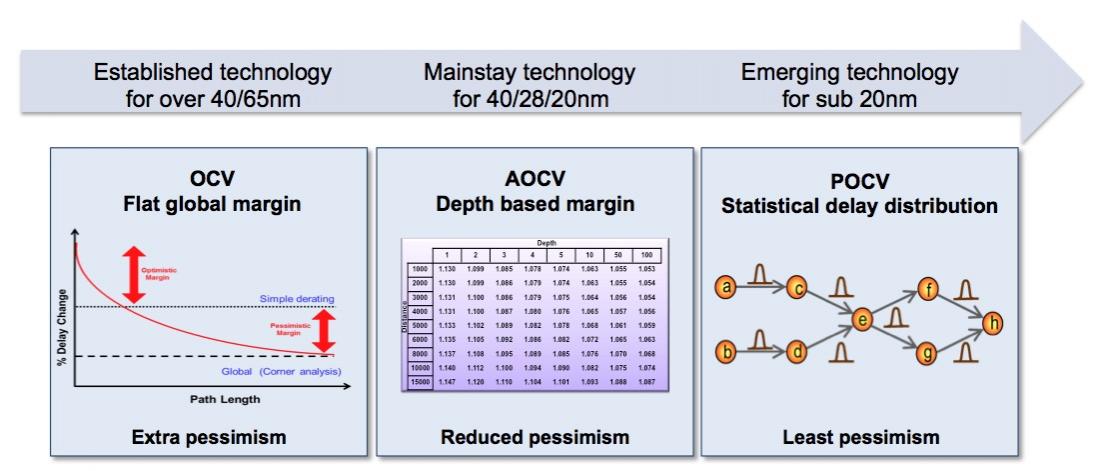

On-chip Variation (OCV) for timing margins and analysis has migrated to Advanced OCV (AOCV) and now Parametric OCV (POCV) as process nodes have moved to 20nm and smaller.

The POCV approach uses a statistical number called sigma, specific to each cell in the library. PrimeTime ADV propagates the sigma value along the graph, and is the least pessimistic which means fewer violations in timing and a faster time to closure. Synopsys contributed changes to the Liberty Variance Format (LVF) and was approved as part of an IEEE standards process, where there are about 20 members.

Learning

For users of PrimeTime SI there is a quick learning curve when adding on PrimeTime ADV. Contact your local AE, or try the tutorial, demo, apnote or online examples. Another good place to learn more is at a PrimeTime SIG event, and the next one is at DAC. Webinars are helpful, and you can view these in both English and Mandarin.

Share this post via:

Comments

0 Replies to “What’s New with Static Timing Analysis”

You must register or log in to view/post comments.