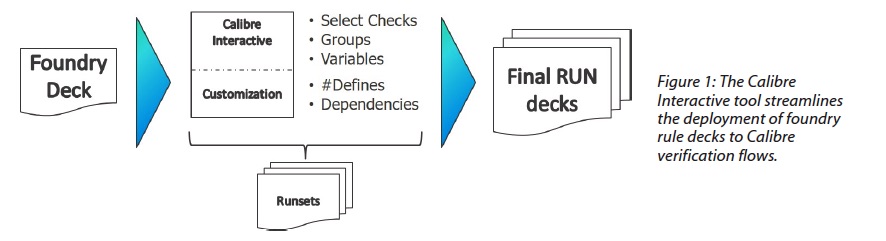

All semiconductor design work today rests on the three-legged stool of Foundries, EDA Tools and Designers. Close collaboration between the three make possible the successful completion of ever more complex designs, especially those at advanced nodes. Perhaps one of the most critical intersections of all three is during physical and circuit verification. IC verification configuration involves selecting the right foundry design rules, selecting verification tool options, managing design related inputs such as libraries, design data scope and location, and managing verification tool output. To facilitate this process Mentor has developed Calibre Interactive, which includes a GUI based interface for managing the execution of the Calibre tool suite.

Mentor has written a paper that includes a high-level description of Calibre Interactive that talks about how it aids CAD engineers and designers by making verification flow set up and execution much easier and highly reproducible. The tools that are managed by Calibre Interactive include Calibre nmDRC, Calibre nmLVS, Calibre PERC and Calibre xRC/xACT.

Mentor paper cites runsets as one of the key features of Calibre Interactive which are used to encapsulate setup data and options. They serve as templates to simplify configuration, maintenance and reproducibility. Different runsets can be created for each of the different tasks that Calibre is used for, such as LVS, extraction, DRC, etc. Also, they can account for the needs of various design flows, including analog, SOC, library development, etc. With runsets many of the complex and error prone aspects of launching a verification run can be standardized and easily utilized.

One example that is given in the paper is how, for instance, specific recipes can be created for use at the cell level that exclude checks that are only applicable at the block or top level. These might be context-based checks such as connectivity and density checks. This helps avoid copious false errors that can clutter up error reports. Calibre Interactive includes an easy to use recipe editor. Recipes can be added to runsets. Also, runsets can easily be shared, making deployment within large companies straightforward.

Calibre verification runs can be customized in a single GUI, avoiding the problem of having the parameters for each run spread out in different locations. Because all available options are shown, less time is spent looking through documentation to see what options apply for a particular PDK. CAD groups can augment Calibre Interactive with Tcl scripts. This makes it possible to only reveal secondary options if the primary option is selected. Internal and external triggers are available to control the execution of scripts. The setup of triggers is also handled through the GUI, which makes it easy to manage and understand.

The paper also lays out a vision for future features that would make it even easier to set up and manage an IC verification environment configuration. Mentor won designers over to Calibre years ago with breakthrough performance. As they have continued with leading performance and capability improvements, they have also chosen to invest in usability. Far from being a convenience feature, design results depend on the ability to consistently and efficiently apply verification tools and flows. Mentor’s Calibre Interactive is proof that they understand the need for this. The paper is available for download on the Mentor website.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.