Hierarchy is used in IC designs at many abstraction levels to help describe a design in a compact format:

- Mask Data

- IC Layout

- Schematic Netlists

- Gate level netlists

- RTL netlists

But the question and focus for this blog is, “What is a hierarchical SPICE Circuit Simulator?”

To me a hierarchical circuit simulator has a few defining characteristics:

[LIST=1]

The only SPICE circuit simulators that fit this hierarchical description are:

- HSIM from Synopsys

- UltraSim from Cadence

- Turbo MSIM from Legend Design

When I last wrote about circuit simulation at Cadence there was some follow-up from Mentor Graphics by Mary Rayburn to clarify what Eldo Premier can do.

Q&A From Mentor about Eldo Premier

Q: When I think about hierarchical circuit simulation I’m looking at a technology that exploits hierarchy like HSIM, XA and UltraSim.

A: HSIM, XA or Ultrasim do not ‘own’ the notion of hierarchy, and all 3 of them uses it in different ways. Eldo Premier is a fully hierarchical simulator, but does not use the notion isomorphic matching (like hsim), that is incorrectly tied to the notion of hierarchy in the minds of many people.

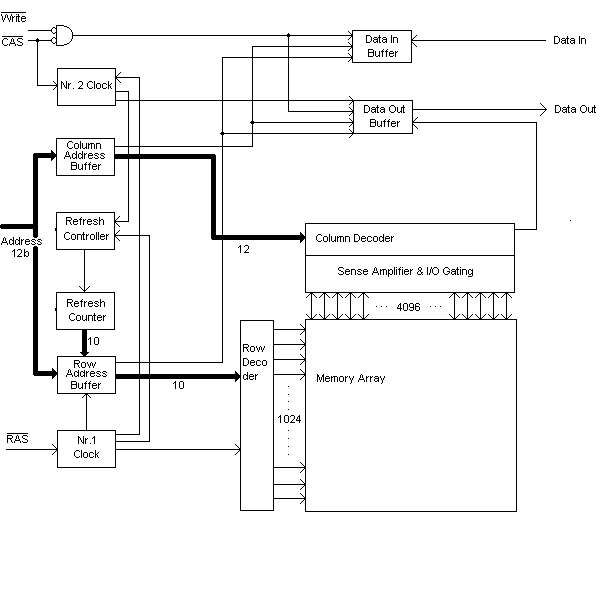

Eldo Premier uses a full hierarchical solver, that has zero commonality with the flat solvers in Eldo Classic, HSPICE or Spectre. The circuit is decomposed in a hierarchical way, using the original netlist hierarchy if any as an initial guess, but most of the times re-building an internal hierarchical representation, using rather complicated graph theory. The main purpose of this hierarchical approach is to speed-up the resolution, both on one core and on multiple cores. The workload distribution is indeed much more efficient with the hierarchical solver compared to a flat one, where in reality only the device evaluation part is efficiently multi-threaded. The purpose of Eldo Premier is not to simulate ‘billions’ (really ?) of transistors in a DRAM.

Q: Sub-linear memory usage as your design size increases. Going from a 1Mbit memory netlist to a 2Mbit netlist takes less than double the RAM to simulate.

A: Eldo Premier has indeed a roughly linear memory consumption with highly hierarchical or repetitive circuits. However many mixed signal circuits with extracted parasitics have a profile where most devices are in fact unique (it is possible to be much more aggressive and silently consider that ‘almost identical’ instances can be merged, and thus save even more memory, but Eldo Premier does not do that, more conservatively).

Q: Only the active memory cells are actually simulated, the inactive cells are left dormant.

A: The hierarchical approach allows to indeed simulate the active parts only, and to take advantage of ‘dormant’ cells (as entire sub-hierarchies) much more efficiently than flat simulators, which can only perform low-level device bypass.

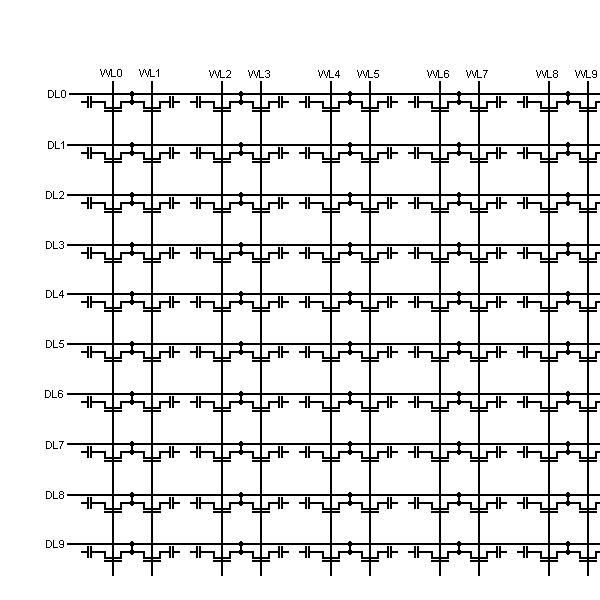

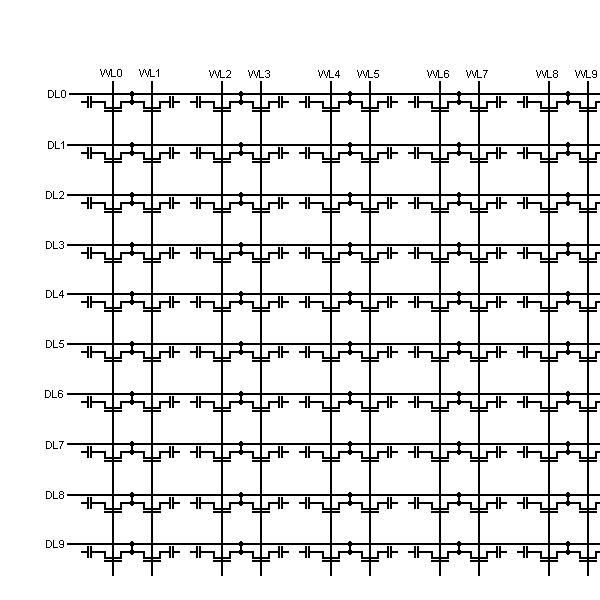

Q: Able to simulate billions of transistors for memory designs: SRAM, DRAM, FLASH

A: These are HSIM claims. The only ‘circuit’ with billion elements that HSIM runs, to our knowledge, is actually a dummy resistor ladder circuit, built for the purpose. Nowadays neither HSIM nor Ultrasim claim billion MOS capacity. Looking at the circuits we receive, customers seems to struggle a lot with circuits in the range of 10M to 100M, whatever the tool they use…

In any case, Eldo Premier’s main target is not these very special circuit cases, but rather ‘large general purpose analog and mixed-signal circuits where the accuracy cannot be compromised’. And the hierarchical approach was absolutely key to deliver speedup ratios in the range of 2x to 15x compared to Eldo Classic for these types of circuits.

Q: If Eldo Premier can do all three of the listed items then I consider it a true hierarchical circuit simulator.

Flat circuit simulators will read a hierarchical netlist but then they flatten the design to simulate it, thus not taking any advantage of the hierarchy.

A: Absolutely. And Eldo Premier does not belong to this class. It reads a netlist, builds a hierarchical representation of the circuit, and takes advantages of the hierarchy by sharing descriptors and solvers, selectively activating/deactivating ‘dormant’ sub-hierarchies, and performing hierarchical workload distribution on multiple-core machines.

Summary

Eldo Premier from Mentor does exploit some hierarchical aspects of a transistor-level netlist but not all that HSIM, UltraSim and TurboMSIM are able to. When it comes to SPICE circuit simulators you have many choices and technologies to choose from. Check out the Wiki page listing all SPICE, FastSPICE and Analog FastSPICE tools known.

Comments

0 Replies to “What is a Hierarchical SPICE Circuit Simulator?”

You must register or log in to view/post comments.