Functional and physical verification are easily the two long poles in most IC product developments. During a design implementation cycle, design teams tend to push physical verification (PV) step towards the end as it is a time consuming process and requires significant manual interventions.

Functional and physical verification are easily the two long poles in most IC product developments. During a design implementation cycle, design teams tend to push physical verification (PV) step towards the end as it is a time consuming process and requires significant manual interventions.

PV Challenges

In the traditional physical design flow, design teams send their designs through a full DRC (Design Rule Check) verification run after completing the place and route step. This process can take several hours for a billion-transistor design and often uncover problems in the design, which must be fixed to comply with foundry manufacturing rules. Subsequent fixes of the errors necessitate a repeat of place-and-route and a full DRC run again. It is quite common to find the fixes introduce yet additional errors, leading to even more iterations and delays before converging on a clean design as illustrated in figure 1a.

Recent complexity of the advanced process nodes has prolonged the physical verification cycle time further as they are accompanied by an increased list of complex DRC rules to satisfy. The advanced nodes had also introduced a finer layer stack segregation namely FEOL, MEOL, BEOL (Front, Middle and Back- End-Of-Lines). For example, DRC errors such as implant related violations on FEOL layers now need to be handled by the place and route system as it correlates with cell placement.

Prior attempts to mediate DRC fixing has been done. One approach is accomplished by facilitating the needed steps for importing and viewing of DRC errors in the P&R environment. Another is by embedding layout editor with the P&R environment to enable custom fixing at the end of DRC run. However, neither of these address the overall cycle time reduction nor the recurring iterations.

Shift Left and Tool Integration

The notion shift left was initially popular in the verification domain and is becoming a mantra to most of EDA tool providers. With ample availability of fast compute resources and more efficient algorithms, it is more practical to provide concurrency access to many solutions previously done as separate processes.

Like the Berkeley’s SPICE and its derivatives in circuit simulation domain, Calibre has been the de facto physical verification tool for over a decade. Now Mentor, a Siemens business, launches a new Calibre based solution dubbed Calibre® RealTime Digital (RTD) – a new physical verification tool that works in concert with popular commercial place-and-route environments.

As design teams use place-and-route to fix violations discovered after full DRC runs, they can use the Calibre RTD tool to make minor changes, thereby resolving DRC violations without causing additional violations — ergo “Correct by Calibre”. Calibre RTD achieves this by making the minor changes and performing customized, smaller and more localized DRC runs to help ensure the violations are removed.

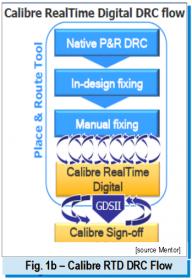

As illustrated in figure 1b, shorter iterations during debug reduce the total number of full-chip pass iterations, allowing designers to dramatically shorten design cycles and get to market sooner. “Calibre RealTime Digital is a solution that was driven by customer requests,” said Joe Sawicki, vice president and general manager of Mentor’s Design-to-Silicon Division.

As illustrated in figure 1b, shorter iterations during debug reduce the total number of full-chip pass iterations, allowing designers to dramatically shorten design cycles and get to market sooner. “Calibre RealTime Digital is a solution that was driven by customer requests,” said Joe Sawicki, vice president and general manager of Mentor’s Design-to-Silicon Division.

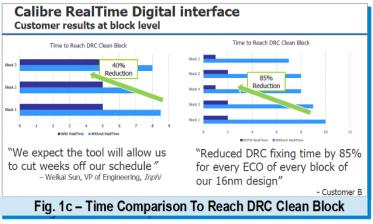

This roll-out is complementing its earlier 2011 release of Calibre RealTime Custom tool for custom IC design flows. RTD targets the full-chip and block-level digital designs and provides teams designing primarily ASICs and SoCs for various electronics end markets. According to Mentor’s early customers feedback, RTD significantly cut the amount of time needed to reach a DRC clean block. Time saving is ranging from 40% for a design block and up to 85% for ECO’ed block.

“The tool can save time and headaches for design teams developing system chips using any digital process. By working in tandem with the place-and-route tool, Calibre RealTime Digital helps correct physical violation errors that cannot be corrected using a place-and-route system alone. As a result, customers have the potential to get designs to market weeks faster,” Joe added.

Endorsements were already given by several named customers such as Qualcomm and Inphi. “Calibre RealTime Digital is an accelerator to our existing physical verification strategies that fits seamlessly into our design flows, We expect the tool will allow us to cut weeks off of our signoff schedule.” said Weikai Sun, associate vice president of Engineering at Inphi.

RTD and P&R

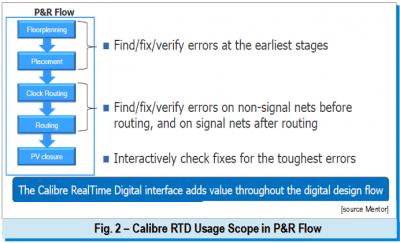

Enabling RTD physical verification in the RTL-to-GDS2 flow include the following usage scenarios. As illustrated in figure 2a, with RTD designers could do DRC early-on at floorplanning stage, during which an optimal IP or macro placement exploration is being exercised and data flow being analyzed.  Furthermore, this also provides a more concrete assessment of area versus performance trade-offs for an IP block during process retargeting. Metal stack selection and routability study are commonly made during this stage in which a balance of route resources for both signal route versus global signals (power, ground and clock networks) is targeted.

Furthermore, this also provides a more concrete assessment of area versus performance trade-offs for an IP block during process retargeting. Metal stack selection and routability study are commonly made during this stage in which a balance of route resources for both signal route versus global signals (power, ground and clock networks) is targeted.

Another challenge faced during P&R stage is in dealing with preemptive placements (such as clock headers, special cells) and routings of critical nets (pre-routes) which often times performed by means of augmented internal script-based tool into the formal flow. These preemptive placements or routes may not satisfy all the DRC complex requirements (for example with respect to metal vs via allocation, cut-metal, etc.). Calibre RTD interface lets designers interactively verify DRC, multi-patterning, and pattern matching fixes in P&R using the same sign-off Calibre decks. Hence, these pre-routes or pre-placements could be ascertained as DRC clean prior to setting any dont-touch attribute on the entities.

RTD Usage Models

With Calibre RTD, physical designers are no longer in need of RVE or RealTime-RVE to interface with Calibre verification. Instead, physical verification can be done in physical implementation environment of choice. Some designers who had used Mentor’s Olympus-SoC might be familiar with earlier Calibre InRoute integration.

This time the level of integration is made across major P&R tools.

This time the level of integration is made across major P&R tools.

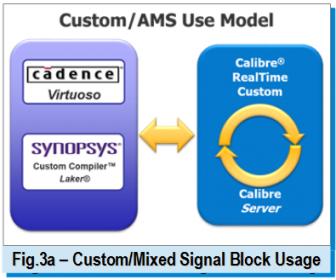

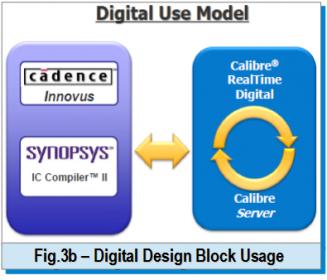

For custom or mixed signal IPs development, the interaction with either Cadence Virtuoso or Synopsys Custom Compiler is supported as shown in figure 3a. On other hand, for ASIC/SOC physical designers integration with Cadence Innovus and Synopsys ICC2 is available as shown in figure 3b.

With the Calibre RTD release, Mentor has upped the ante in tackling design cycle reduction by doing a shift-left and integrating Calibre physical verification to be part of design implementation. Mentor has reported no meaningful memory footprint impact as RTD should be able to be run on any design size being routable by designers P&R of choice.

Several customer DAC 2018 presentations are scheduled at Mentor’s booth #2621. For more detailed info on Calibre RTD, please check HERE.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.