One of the surprises at DAC for ICScape was to be listed on Gary Smith’s list of companies to see. Surprised, since ICScape had never presented their products to him. They were listed under design debug. They don’t have a single product that really falls under that description, but rather a family of tools under the ICExplorer family such as ClockExplorer.

Part of the family is a tool for interconnect analysis which is called RCExplorer. Although like any tool it can be used for many things (who hasn’t put in a screw using a hammer?) it is targeted at 3 main functions:

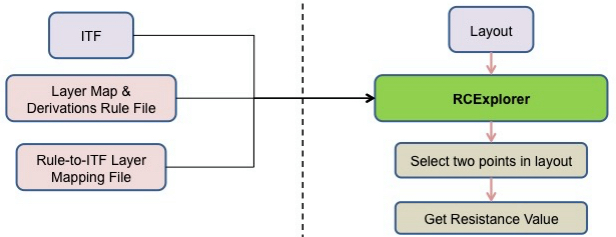

- fast resistance/capacitance analysis which works with popular layout editing tools

- post-extraction interconnect analysis

- interconnect comparison of different versions of a design

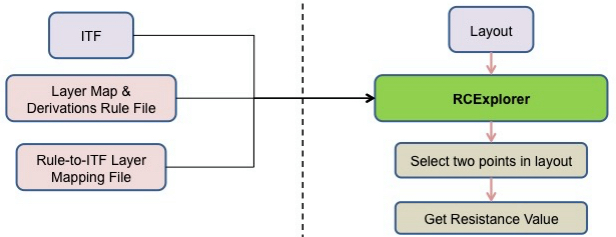

RCExplorer works with popular layout editing tool environment, and is also tightly integrated into ICScape’s own chip finishing environment Skipper. It gives a way to do a quick analysis of interconnect during design, looking for high resistance paths that might lead to ESD problems, or to differential paths that should have the same resistance, and more. To do this does not require the user to run a time-consuming LVS and full extraction, RCExplorer does what is necessary under the hood starting from the layout itself. At its most basic the user can select two points on the layout and RCExplorer will display the resistance between them, giving the resistance by segment/layer/location. When used within the Skipper platform, which has fast net-tracing capability, RCExplorer can provide flexible point-to-point analysis for large nets, such as power and clock nets, completely or partially, for interactive usage.

RCExplorer works with popular layout editing tool environment, and is also tightly integrated into ICScape’s own chip finishing environment Skipper. It gives a way to do a quick analysis of interconnect during design, looking for high resistance paths that might lead to ESD problems, or to differential paths that should have the same resistance, and more. To do this does not require the user to run a time-consuming LVS and full extraction, RCExplorer does what is necessary under the hood starting from the layout itself. At its most basic the user can select two points on the layout and RCExplorer will display the resistance between them, giving the resistance by segment/layer/location. When used within the Skipper platform, which has fast net-tracing capability, RCExplorer can provide flexible point-to-point analysis for large nets, such as power and clock nets, completely or partially, for interactive usage.

The way it works is to extract the segment resistances of the whole net using patterns, add virtual current sources at the two specified points, compute voltage at points using a high-performance matrix solver and then get the equivalent resistance between the two points based on voltage/current values. It only performs extraction once per net, so it it fast to do resistance analysis for multiple points on the same net.

The way it works is to extract the segment resistances of the whole net using patterns, add virtual current sources at the two specified points, compute voltage at points using a high-performance matrix solver and then get the equivalent resistance between the two points based on voltage/current values. It only performs extraction once per net, so it it fast to do resistance analysis for multiple points on the same net.

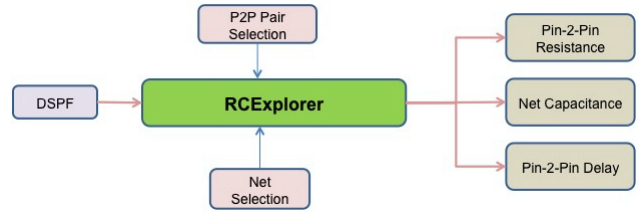

The next use-model is post extraction. Instead of doing its own layout analysis, RCExplorer reads in the DSPF parasitic file directly. It then reports:

The next use-model is post extraction. Instead of doing its own layout analysis, RCExplorer reads in the DSPF parasitic file directly. It then reports:

- pin-to-pin resistance

- net capacitance, both total and coupling

- pin-to-pin delay on the flattened design

- it can run analysis on either selected nets, using filters, or on all nets

- it can run analysis on a selected pin pair or on all pin pairs

- it can handle the largest nets: power, ground, clocks etc

If the DSPF file contains layout information for the nodes and RC devices, RCExplorer can also do cross reference between layout-editing tool and the analysis result, very useful during post-layout debugging.

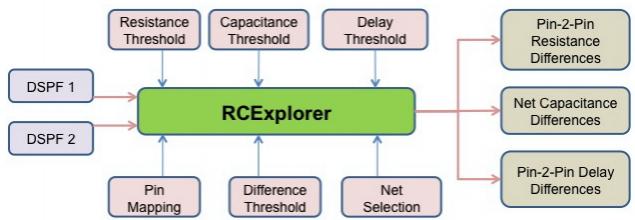

The final use model is to compare two versions of the same design at the DSPF level. The normal way to do this is to set some filter, and get RCExplorer to identify, for example, all nets that have changed by more than 5%. The same analysis can be used to compare two different extractions with different tools, looking for nets where the two extractors are off by more than a trivial amount. The error distribution can be displayed either graphically or in tabular format.

The final use model is to compare two versions of the same design at the DSPF level. The normal way to do this is to set some filter, and get RCExplorer to identify, for example, all nets that have changed by more than 5%. The same analysis can be used to compare two different extractions with different tools, looking for nets where the two extractors are off by more than a trivial amount. The error distribution can be displayed either graphically or in tabular format.

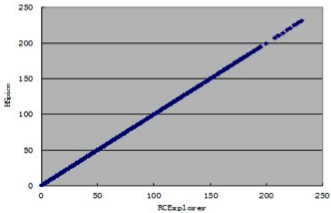

A tool like RCExplorer is only useful if it is accurate. Comparing its calculations to a “golden” HSPICE simulation over thousands of pin-pairs in a design shows the accuracy is 0.005% (so 0.00005 which has to be in the noise).

A tool like RCExplorer is only useful if it is accurate. Comparing its calculations to a “golden” HSPICE simulation over thousands of pin-pairs in a design shows the accuracy is 0.005% (so 0.00005 which has to be in the noise).

The analysis is also fast because the use of advanced matrix solver technology and reuse of analysis models. Analyzing a 343 net design (60K pin-pairs) with a 1GB DSPF took just 1 minute 38 seconds. Analyzing a design with 265K nets (21M pin-pairs) took 1h 33m from a reduced DSPF and 6h 12m from a non-reduced DSPF.

RCExplorer is in full-release. It is in use at several customers including a major flash-memory company. They haven’t given permission to use their name so you will have to make your own guess as to which one.

See also How Good Are Your Clocks?

See also What is Skipper?

The RCExplorer product page is here.

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era