“Power is the new timing” has almost become a cliché. There are a number of reasons for this, not least that increasingly it is power rather than anything else that caps the performance that a given system can deliver. Power is obviously very important in portable applications such as smartphones because it shows through directly in parameters like standby-time and talk-time that consumers use to guide their purchases. But even tethered applications are increasingly limited by power, either at the chip level for factors like being able to use a cheap package, or at the massive system level where server farms are increasingly limited not by the size of the systems but the ability to get enough power into and out of the building.

In the past we had a big tool for fixing power issues: lower the supply voltage. But we can no longer do that for various technical reasons around leakage and noise margin.

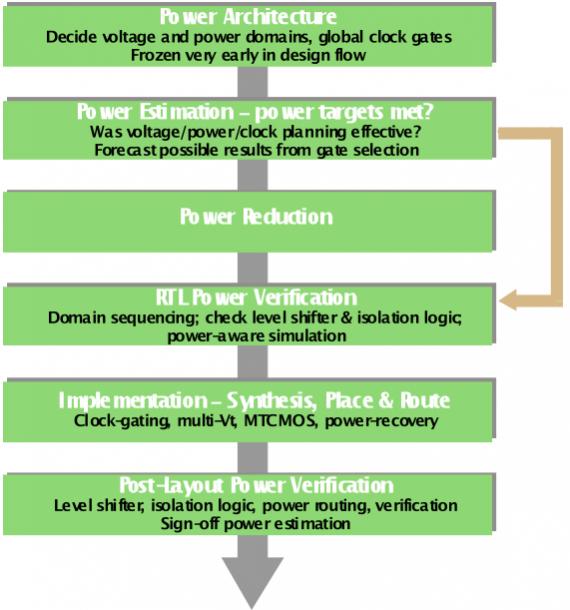

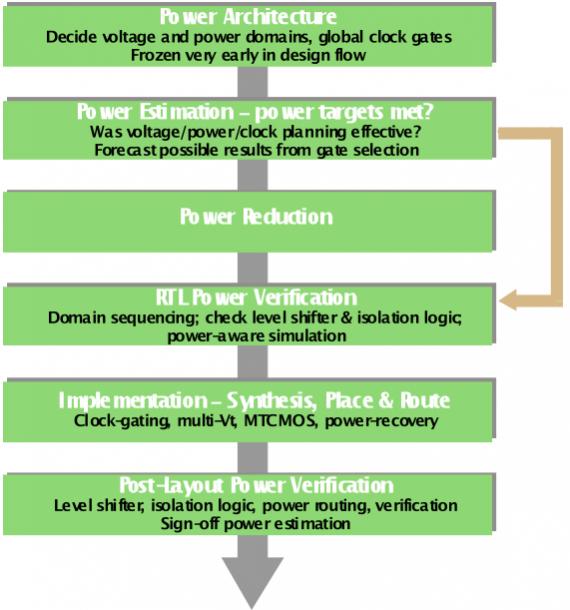

Power is a chip level problem that must be addressed at multiple levels to be effective. Since power needs to analyzed early in the design cycle, the first issue is being able to analyze power at the RTL level so that the effectiveness of various potential changes can be evaluated.

The arsenal of weapons that can be brought to bear on power reduction include:

Multi-voltage threshold libraries Since leakage current is an increasing part of the problem, it is good to use high-threshold, low-leakage, low-performance cells on non-critical nets, and keep the low-threshold, high-leakage, high-performance cells for the timing critical parts of the design. Early in the design an estimate of the ration of the two cell-types can be used to guide computation of power consumption since the precise selection of cells will be done by the synthesis tool later.

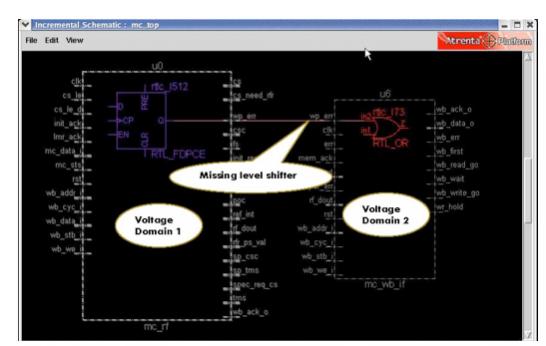

Voltage domainsOften some parts of the design are much more critical for power or timing than others and so the design can be separated into separate voltage domains. CPF and UPF standards are a way to capture this data and ensure that all tools handle level shifters and isolation cells properly. Of course, areas can be powered down too, but this is something above the level of the SoC itself, typically controlled by quite a high level of the control software (are we making a phone-call now? Is an mp3 being played?).

Clock gating In the past the golden rule was never to gate a clock. Instead, a register containing an unchanging value was looped back to its input through a multiplexor. Now, in the low power era, that structure is best replaced with a gated clock, especially if the register is large (since the clock can be gated for the entire register rather than for each flop in the register). There are further opportunities for power saving since a register fed by an unchanging register cannot change on the following clock cycle, for example.

Activity management Optimizing the clock is an important part of power management because clocks are the most active nets in the design (they change on every clock cycle, surprise) and they are large so also account for a lot of the capacitive load in the entire design. By gating clocks further up the clock-tree the power consumed in the clock itself can often be greatly reduced.

Verification Most of the changes discussed above require changes to the design that have the potential for error and so they need to be verified at both the netlist and the post-layout stages.

SpyGlass-Power takes in the design at the RTL stage, analyzes for power holes, suggests changes and even automatically fixes power issues. Packed with an integrated design creation environment, it offers designers a platform to create power-conscious RTL right from the very beginning of the design process.

References:

SpyGlass-power white papers

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era