Digital design engineers have used DFT automation technologies like scan and ATPG for decades now, however, analog blocks embedded within SoCs have historically required that a test engineer write tests that require specialized expertise and that can take man-months to debug. Siemens has a long history in the DFT field, SPICE circuit simulation and AMS simulation, so it was a natural fit for them to announce analog component testing as part of a new product dubbed Tessent AnalogTest. I had a video call with Etienne Racine, Product Manager, Tessent to understand what’s new.

Testing analog components inside an SoC drives up the test costs, so there’s impetus to reduce this time through automation techniques. Scan for digital has now been extended into the analog realm. There’s an that talks about a novel DFT and ATPG technique that has minimal area and performance impact, and Tessent AnalogTest uses it as part of its technology.

Using such scan-based analog tests reduces defect simulation times from days to minutes and brings to analog very similar benefits as what digital scan and ATPG provided to digital designs several decades ago. Leveraging evolutive standards thus becomes important for broad adoption and EDA industry support.

IEEE P2427 is both a working group and draft standard that gives a standardized approach for analog defect modeling and coverage in Analog Mixed-Signal (AMS) devices, where the defect universe contains all likely defects, and also defines detectable defect coverage. The test idea is to inject a defect in the netlist, run a SPICE circuit simulation and then measure the effects to see whether the resulting fault is detected.

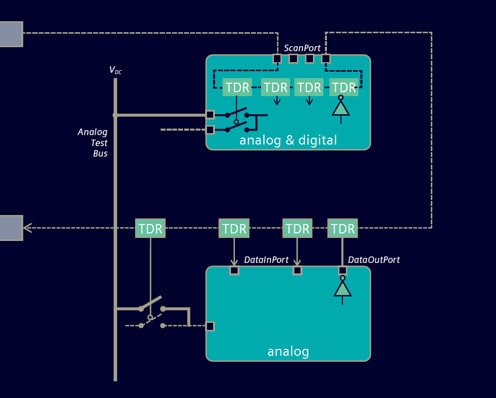

Users of Tessent AnalogTest can also use the IJTAG framework to enable portable and retargetable AMS function tests, defined in the IEEE P1687.2 standard. There’s a learning curve with the Instrument Connectivity Language (ICL) and Procedural Description Language (PDL) to describe the analog test access, instruments and analog test mechanisms. The automation helps users to create those files when they don’t already exist.

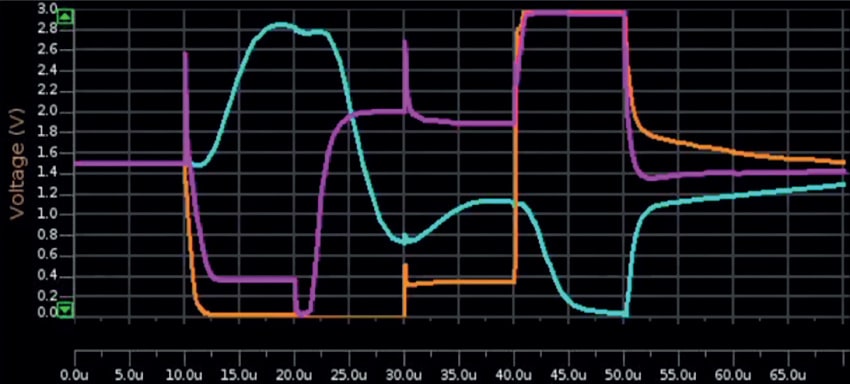

Test engineers write PDL for the AMS block, like force 2.5V on this pin, then measure the current on another pin. Tessent AnalogTest reads the PDL file, then creates a simulation test bench automatically. The Siemens tool also reads in the SPICE netlist for the AMS blocks, runs the SPICE simulator to detect injected defects, then reports coverage achieved. Two Siemens simulators are supported for analog defect/fault simulation and detection, AFS or Symphony.

This new approach with Tessent AnalogTest combining digital scan-based tests and analog IJTAG measurements improves AMS test coverage plus reduces test development and application times. When silicon arrives, your team can optimize defect coverage or yield, eventually extending this to automated defect analysis. Safety critical applications that use ISO 26262 functional safety metrics will benefit from this approach with a consistent, simulated, automated test description.

Learning and using the high-level PDL language to describe intended test sequences is a big time saver, freeing up engineering resources. IJTAG is well understood by test teams, so expanding that to include analog blocks is an easy process. The Tessent AnalogTest tool automates the creation of DFT circuitry along with test patterns to test most analog circuits in under 1ms on digital-only testers. Even the test times get reduced 10X-100X while providing similar defect coverage to specification tests.

AMS designs now have new automation technology to dramatically improve analog test development and reach coverage goals, while being connected with IJTAG scan chains and an analog test bus. Siemens has introduced something not seen before, so it’s exciting times. Following the IEEE standards P2427 and P1687.2 ensures that this technology will be supported by the EDA industry going forward.

Related Blogs

- Siemens EDA and Nvidia: Pioneering AI-Driven Chip Design

- Siemens Describes its System-Level Prototyping and Planning Cockpit

- New Product for In-System Test

- AI-Powered Transformation in EDA

- Enabling Imagination: Siemens’ Integrated Approach to System Design

Comments

There are no comments yet.

You must register or log in to view/post comments.