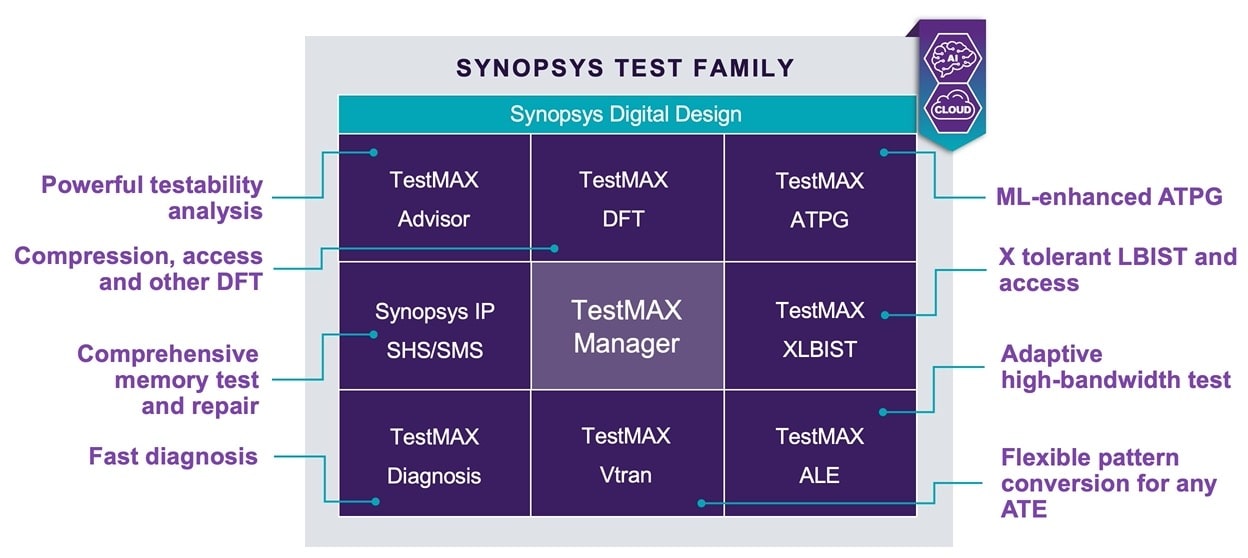

I recall an early custom IC designed at Wang Labs in the 1980s without any DFT logic like scan chains, then I was confronted by Prabhu Goel about the merits of DFT, and so my journey on DFT began in earnest. I learned about ATPG at Silicon Compilers and Viewlogic, then observability at CrossCheck where I met Jennifer Scher, now she’s at Synopsys. We talked last week by video along with Synopsys Product Manager Ramsay Allen, who previously worked at UK IP Vendor Moortec, another SemiWiki client acquired by Synopsys. Test expert and R&D Director, Chandan Kumar also joined the call. Over the years Synopsys has both acquired and developed quite a broad range of EDA and IP focused on testability, so I’d say yes, they are ready for DFT.

Our discussion centered on the TestMAX Advisor tool and how it helps on testability issues that can be addressed early at the RTL stage, like:

- DFT violation checks – ensures RTL is scan ready

- ATPG coverage estimation – does RTL design achieve fault coverage goals

- Test robustness – reliability in presence of glitches, Xs, edge inconsistencies

- Test Point selection – finds hard-to-test areas

- Connectivity validation – DFT connections at SoC assembly

The focus of this interview however was the latest test robustness and reliability capabilities that Advisor provides in the form of glitch monitoring and X capture.

Glitches

A digital circuit that produces glitches on certain nets can cause temporary errors, something to be avoided in making an IC operate robustly and reliably. Three classes of glitches can be identified automatically by TestMAX Advisor:

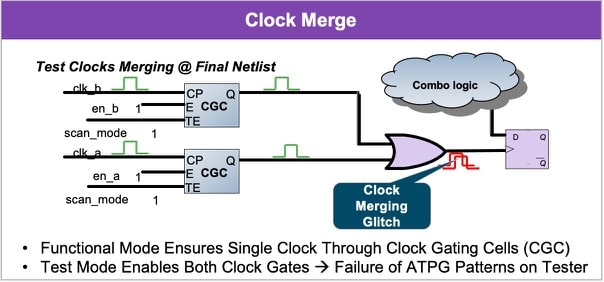

- Clock Merge

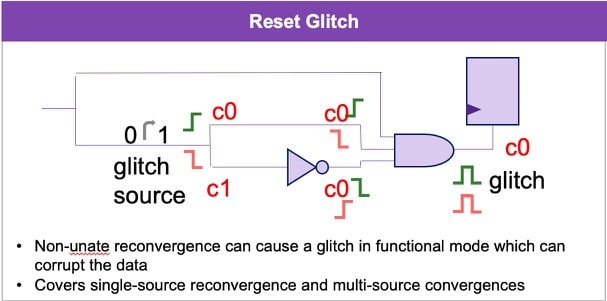

- Reset Glitch

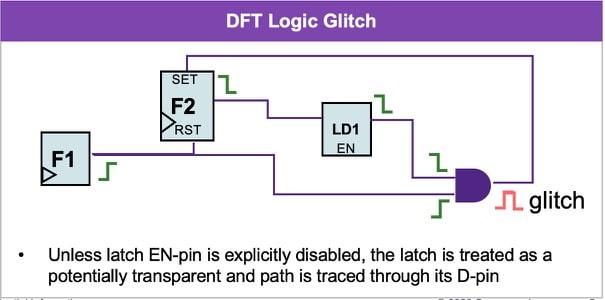

- DFT Logic Glitch

Here’s an example logic cone for each type of glitch:

In functional mode the designer needs to ensure that a single clock passes through the Clock Gating Cells by controlling the enabled pins, but then in test mode only one clock signal can propagate. The above example shows how two clock signals combine to create a clock merge glitch, which needs to be found and fixed before tape out.

Every violation detected by Synopsys TestMAX Advisor includes the RTL source code line number to consider changing, so designers know what is causing the issue. Tool users can even define any logic path between two points in their design to search for glitches. Glitches are painful to find, especially if they aren’t found until late in the logic design cycles or even during silicon debug. Glitches can be triggered on rising or falling edges of internal signals, so it’s paramount to discover these early in the design process when changes are much easier to make. The automated checking understands the unateness of each logic path.

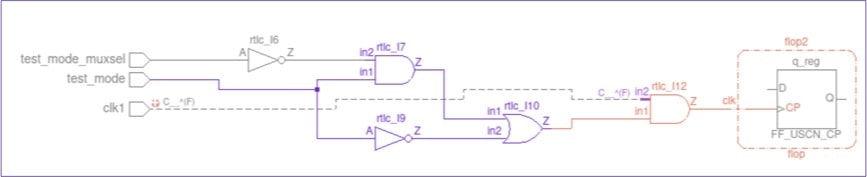

Another example of glitch detection was shown when a signal called test_mode would transition.

The actual error report for this glitch was:

Clock(s) and 1 Clock Enable(s) logic reconverges at or near ‘test.clk_en‘.(Count of reconvergence start points = ‘1’ reconvergence end = ‘test.clk_en‘)[Affects ‘1’ Flip-flops(s)]

The final type of glitch detection was for buses driven by tri-state buffers, where clock edge inconsistencies and bus contention were caught.

Summary

RTL design and debug is a labor-intensive process, so having proper automation tools like Synopsys TestMAX Advisor are an insurance policy against re-spins caused by testability issues like glitches and Xs in an IC design. Early warning on the DFT robustness is a smart investment that pays off in the long wrong by improving the chances for a first silicon success. Design engineers run Synopsys TestMAX Advisor on every level of their hierarchical design, including the final, full-chip level.

Designers save time by using an automated checking tool, instead of relying upon manual detection methods.

For more information on Synopsys TestMAX products, please, visit the website.

Related Blogs

- Takeaways from SNUG 2023

- Use Existing High Speed Interfaces for Silicon Test

- Synopsys Expands into Silicon Lifecycle Management

- Addressing SoC Test Implementation Time and Costs

- Synopsys Enhances Chips and Systems with New Silicon Lifecycle Management Platform

- Accelerating Functional Safety Verification

Comments

There are no comments yet.

You must register or log in to view/post comments.