The growing amount of electronics within today’s automobiles is driving very high quality and reliability requirements to a widening range of semiconductor devices. At the same time, traditional fault models are becoming less effective at achieving desired silicon quality levels. Improvements in test solutions are needed not only to maintain very high quality levels in more advanced technology nodes, but to also address the increasing reliability requirements defined within the ISO 26262 standard.

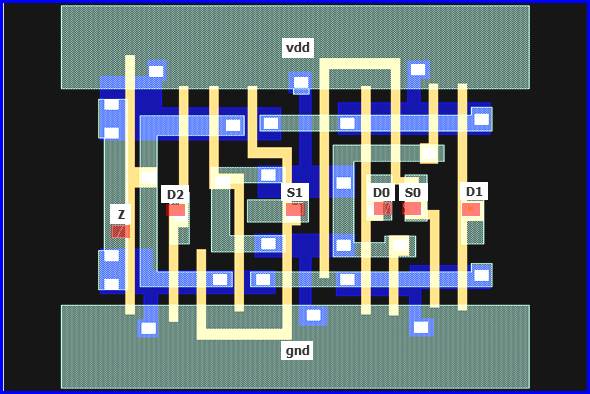

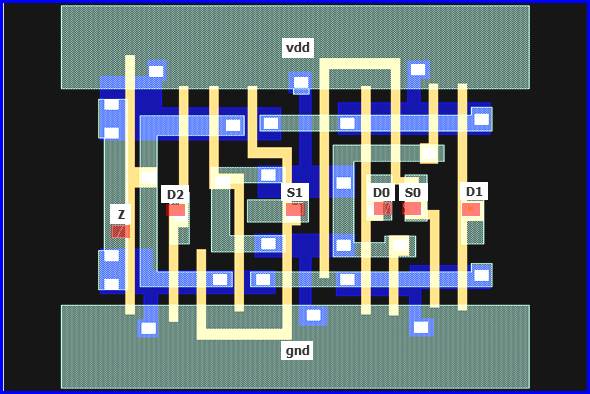

A new seminar from Mentor Graphics’ Semiconductor Test Solution group explains the latest approaches in testing automotive semiconductors. It will cover details of the new cell-aware test methodology, whichmodels and targets defects within each cell, addressing the inherent limitations of traditional testing. Call-aware testing has been shown to significantly reduce DPM levels in shipped devices.

The seminar will also cover the cell library characterization flow, which creates new cell-aware fault models and is a key element of this methodology. Pattern and coverage results for several industrial designs will be presented as well as silicon test results gathered from several million parts. Cell-internal diagnosis and physical failure analysis results will also be demonstrated to show how cell-aware tests can help detect the root cause of physical defects.

To further expand your test repertoire, the seminar will also cover the IEEE P1687 (IJTAG) standard and how it can help you test the increasing number of digital and mixed-signal embedded IP blocks. Finally, it will describe new hybrid ATPG compression plus logic BIST technology that provides more efficient defect coverage and the ability to apply tests within the system for long-term reliability.If you care about test costs, outgoing product quality levels, diagnosis of semiconductor failures, or maintenance of cell libraries, this seminar will provide you with valuable new approaches to address your testing challenges. June 25 (NA), 26 (Calcutta), 27 (Berlin). Register here…

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.