At DAC in June I first blogged about Symicabecause they offered a Fast SPICE circuit simulator, and today I discovered a free version so I decided to write up a mini-review for you.

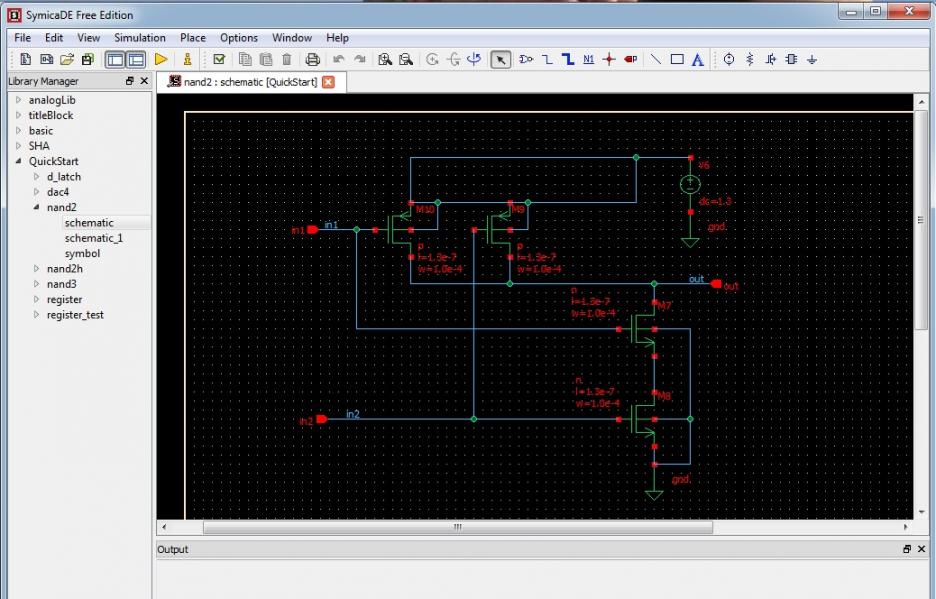

I choose to download and evaluate the Windows version and it installed just fine and invoked quickly. This free version is limited in number of devices and also features, but you still get a good feel for the capabilities. Schematic capture is called SymicaDE and it looks like similar tools from Cadence, Mentor or Synopsys:

Their CMOS library has both 3 and 4 terminal MOS devices, and I was using the 4 terminal devices in the tutorial.

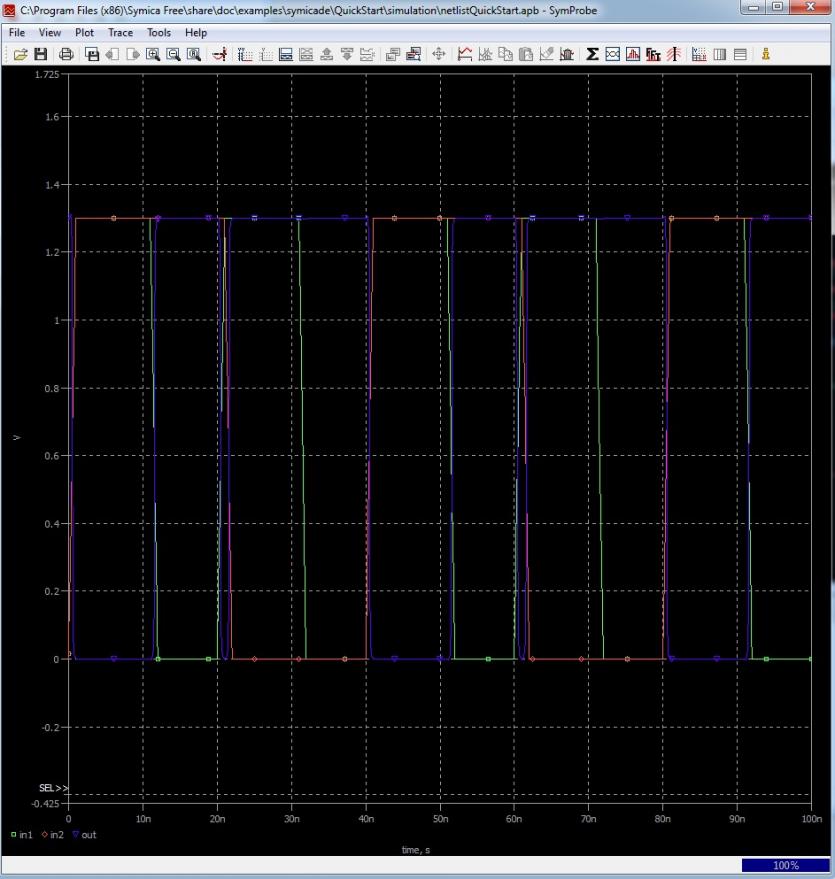

There’s a QuickStart library filled with digital, analog and mixed-signal schematics, symbols and code. A PDF document for Quick Start is useful and within a few minutes I was simulating a 2 input NAND gate in their SPICE tool an viewing the waveforms:

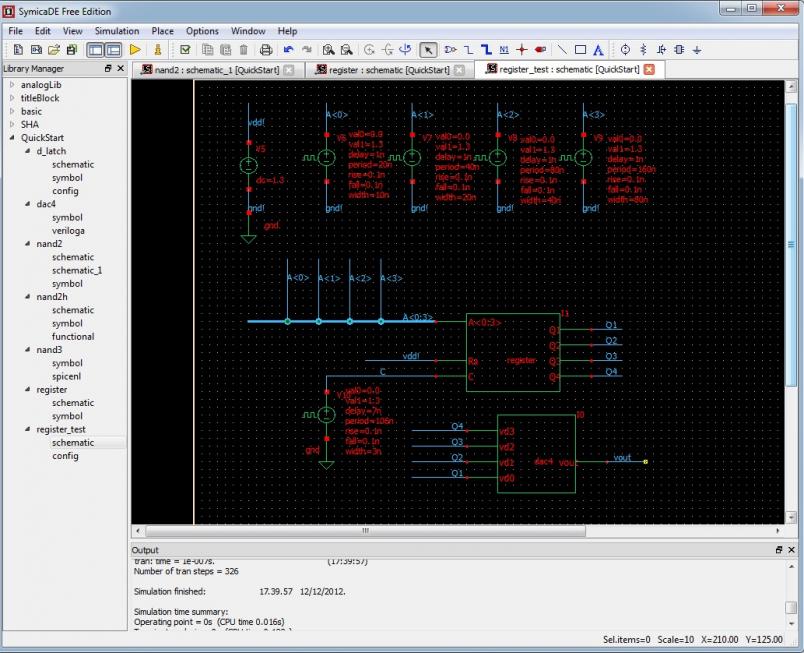

The most complex circuit in the QuickStart library is a 4 bit register connected to a DAC using Verilog A for the DAC:

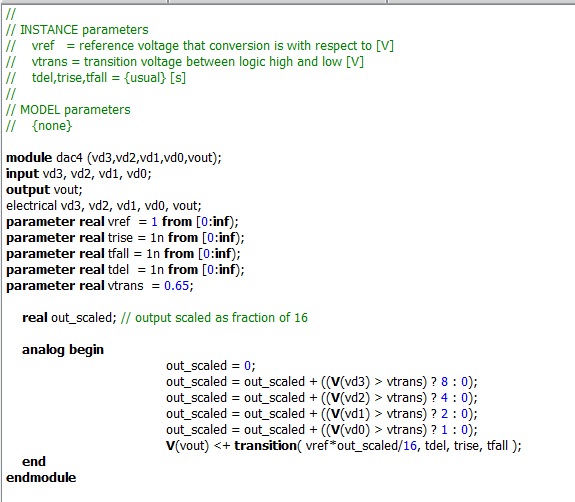

A peek at the Verilog A code for the DAC:

With my Free version I couldn’t simulate Verilog A, just look at it.

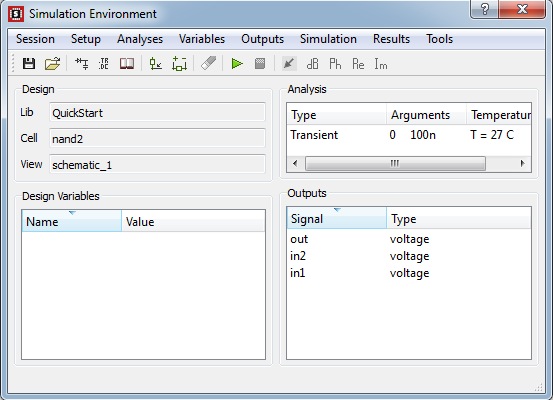

The GUI to control the SPICE simulation was easy to learn and use:

There were only two model libraries to choose from, 130nm and 180nm:

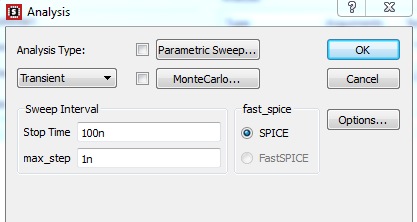

Adding signals to probe in the waveform viewer was a simple click on the schematic, setting up the transient analysis required a total simulation time and max-step:

Symica also has an IC Layout editor called SymLayout, however there were no libraries or cells to play with in my free download.

Summary

Symica pleasantly surprised me with their SPICE circuit simulator, schematic capture, simulation environment and layout editor. Their tools are not full-featured like the big three in EDA, but then again the price is more affordable too. They even have some Cadence SKILL import capabilities.

Symica does have a handful of customer quotes on their web site, mostly from the Kiev area, and time will tell if the IC market starts to evaluate this toolset.

Other reading:

SPICE and Fast SPICE Vendor Wiki

Share this post via:

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era