Linda Fosler, Tom Daspit and Mitch from Mentor Graphics met with me last Monday at DAC to provide an update on IC layout and circuit simulation tools. My notes follow:

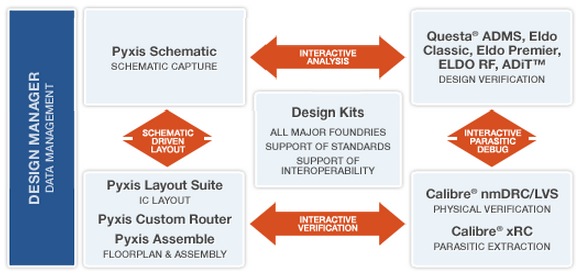

Overview – Pyxis for Schematic and Layout, IC Station is re-branded as Pyxis. (Pyxis schematic is still Falcon, Ample language is still used.)

Pyxis was Open Access, now Falcon-based.

Simulation with Questa (HDL), Eldo Classic, Eldo Premier, ADiT.

Calibre – used for DRC,LVS.

DSM Division – CICD R&D in Wilsonville, Fremont is HQ, Austin is Pyxis router, Grenoble in AMS, Cairo, Armenia, Noida, Taiwan.

Vision – Silicon aware design solutions. AMS has stayed little automated, routing was automated with Pyxis (Marvel uses this and cut tape out time in half).

Technical Advisory Board (TAB). AMS for digital designers, support advanced packaging. ARM, Carelton, CMU, CSR, ST, Infineon, ON Semi, City University.

AMS market – $85B in size: Automotive, identity, security, power, lighting, base stations. Design starts that are AMS is increasing (SOurce: IBS, Dr. Handel Jones). About 70% of all design starts are AMS.

Tom Daspit – Product Manager for Pyxis platform. Schematic, Layout, routing. (Ciranova has only analog placer. Virtuoso is complete, customers can use both tools. Springsoft – strong on layout, weak on schematic. Tanner EDA – OK for cell design, however chip assembly with Mentor.)

– Custom Router

– Calibre RealTime (DRC full checks as you draw). Compaction tried but not effective any more with advanced nodes. In analog shielding is used to keep noise levels down.

Pyxis concurrent – multiple designers work on the same cell concurrently, safely. Checkout design from ClioSOft, then Pyxis manages how to share between team members.

Mitch (Pyxis – acquired in 2010) – Router in use, 28nm designs. TSMC qualified for analog at 28nm.

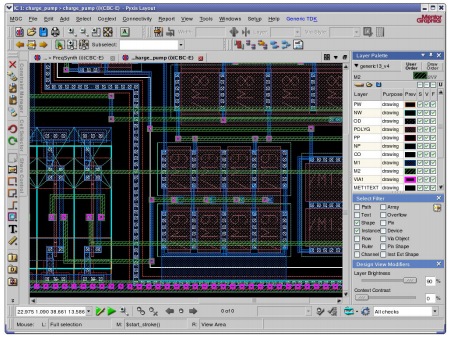

– VCO and differential pair in the demo. Incremental router that gives the designer complete control. User is a layout designer, while the circuit designer provides the constraints. A folded MOS device you want to tie the ends of the poly together, constraints let you specify how that is done. Layout designer may want to add trunks and spines, Pyxis knows how to automate that for you.

– First phase is that Pyxis is using its own DRC checker, Second phase it will start to use Calibre RealTime as the DRC checker. Circuit designer enters constraints using a GUI.

– In a PLL layout there are three voltage domains, PERC will define and enforce these rules. Now adding PERC rules to help constrain analog layout and it creates Pyxis constraints.

IPL wants to standardize analog IPL constraints. If these constraints are standaridized then Pyxis could import them.

GUI for defining constraints. Groups identified by PERC then Pyxis constraints are generated. Analog signal required larger spacing rules to ensure noise immunity.

PERC – used to check that the physical routing was done correctly to match the constraints.

Router talking directly to Calibre RealTime. Demo of an IC layout that wasn’t clean, then re-routed it with Pyxis and Calibre enabled together. Coming in January 2013 release. Calibre-enabled analog routing including coloring rules for DPT.

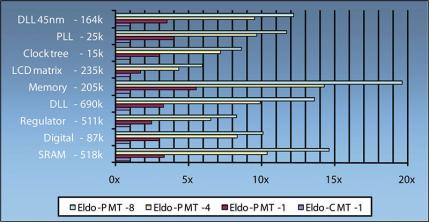

SPICE – Eldo Classic, up to 1M. Analog IP use. Multi-threaded.

– Eldo Premier, Faster SPICE. 2.5 to 20X faster than Eldo, developed internally. Up to 10M nodes. Multi-threaded natively.

– Eldo Premier results: 2.1X to 15X speedup versus Eldo. Premier uses an additional license, it’s just an option when you invoke the simulator. Reads HSPICE and SPectre netlists. Same waveform viewer as Eldo.

– New features: Multi-cpu

IC Scape – One user tried it, now back to Mentor tools.

CiraNova – only an automated placer, not a router. Limited potential.

Summary

Mentor acquired the Pyxis schematic, layout and routing tools and integrated them into their own IC flow so you could use a single EDA vendor for: Architectural Design, functional simulation, IC layout, IC routing, HDL simulation, SPICE simulation, DRC/LVS, Litho, test and tape-out. This appears to be one of the more successful acquisitions by Mentor in recent years. IC layout and circuit simulation are very competitive market segments and Mentor continues to battle against the other EDA vendors by improving their IC flow, deepening the integration with Calibre, and making SPICE faster with increased capacity.

Comments

2 Replies to “A DAC Update from Mentor Graphics on IC Layout and Circuit Simulation Tools”

You must register or log in to view/post comments.