Mentor announced the latest version of their Veloce emulator at the Globalpress briefing in Santa Cruz. The announcement is in two parts. The first is that they have designed a new custom chip with twice the performance and twice the capacity. It supports up to two billion gate designs and many software engineers. Surprisingly the chip is only 65nm but Mentor reckons it outperforms competing emulators based on 45nm technology. I’m not sure why they didn’t design it at 45nm and go even faster, but this sort of chip design is a treadmill and so it is not really a surprising announcement. In fact, I can confidently predict that in 2014 Mentor will announce the 28nm version with more performance and more capacity!

Mentor announced the latest version of their Veloce emulator at the Globalpress briefing in Santa Cruz. The announcement is in two parts. The first is that they have designed a new custom chip with twice the performance and twice the capacity. It supports up to two billion gate designs and many software engineers. Surprisingly the chip is only 65nm but Mentor reckons it outperforms competing emulators based on 45nm technology. I’m not sure why they didn’t design it at 45nm and go even faster, but this sort of chip design is a treadmill and so it is not really a surprising announcement. In fact, I can confidently predict that in 2014 Mentor will announce the 28nm version with more performance and more capacity!

Like most EDA companies, Mentor doesn’t do a lot of chip design. After all they sell software. But emulation is the one area that actually uses the tools. Since one of the big challenges in EDA is getting hold of good test data for real chips, the group is very popular in other parts of Mentor since the proprietary nature of the data is less of an issue inside the same company.

The other thing that they announced is VirtuaLAB. I assumed that this was already announced since Wally Rhines talked about it in his keynote at the Mentor Users’ Group U2U a week or two ago and I briefly covered it here. Historically, people have used an in-circuit-emulation (ICE) lab with real physical peripherals. These suffer from some big problems:

- expensive to replicate for large numbers of users

- time consuming to reconfigure (which must be done manually)

- challenging to debug

- doesn’t fit well with the security access procedures for datacenters (Jim Kenney, who gave the presentation, said he had to get special security clearance to go and get a picture inside the datacenter since even the IT guys are not allowed in)

- is never where you want it (you are in India, the peripherals are in Texas)

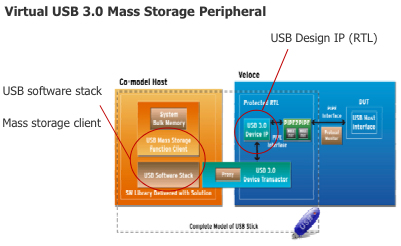

VirtuaLAB is a software implementation of peripherals. They run on Linux and are hardware-accurate. They can easily be shared, after all it’s just Linux. They can be reconfigured by software. You don’t need to go into the datacenter on a regular basis to reboot/reconfigure anything. Of course the purpose of all this is so that you can develop/debug and test device drivers and so on using the models. For example, here is a model of a USB 3.0 Mass Storage Peripheral (aka Thumb drive).

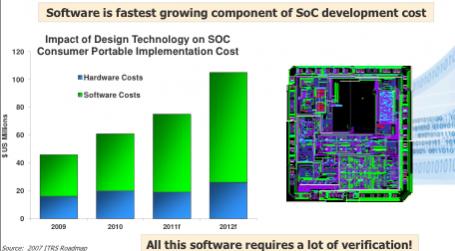

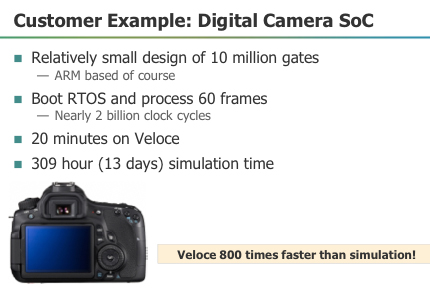

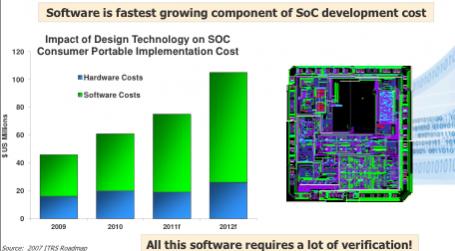

Afterwards I talked to Jim. He confirmed something I’ve been hearing from a number of directions. Although people have been saying for years that simulation is running out of steam and you need to switch to emulation (especially people whose job is to sell emulation hardware), it does finally seem to be true. You can’t do verification of a modern state of the art SoC including the low-level software that needs to run against the hardware, without emulation. For example, a relatively small camera chip (10M gates) requires two weeks to simulate or 20 minutes to emulate.

Afterwards I talked to Jim. He confirmed something I’ve been hearing from a number of directions. Although people have been saying for years that simulation is running out of steam and you need to switch to emulation (especially people whose job is to sell emulation hardware), it does finally seem to be true. You can’t do verification of a modern state of the art SoC including the low-level software that needs to run against the hardware, without emulation. For example, a relatively small camera chip (10M gates) requires two weeks to simulate or 20 minutes to emulate.

I asked him who his competition is. Cadence is still the most direct competition. Customers would love to be able to use an emulator at Eve’s price-point but it seems that for many designs, getting the design into the emulator is just too time-consuming. And EDA has always been a bit like heart-surgery, it’s really difficult to market yourself as the discount heart-surgeon.

I asked him who his competition is. Cadence is still the most direct competition. Customers would love to be able to use an emulator at Eve’s price-point but it seems that for many designs, getting the design into the emulator is just too time-consuming. And EDA has always been a bit like heart-surgery, it’s really difficult to market yourself as the discount heart-surgeon.

Comments

There are no comments yet.

You must register or log in to view/post comments.