The Linley group is the go-to source for information about the microprocessor market. If you go back to their roots in Michael Slater’s Microprocessor Report then they have been in the business for 25 years. We haven’t had microprocessors for that much longer. They just tagged Tensilica as being second in shipments… Read More

It takes an act of Congress…

Foreign students earn roughly two-thirds of the total engineering Ph.D.s earned in the U.S., yet there is no policy to allow, let alone encourage, them to stay in the U.S. after graduation. I was aware of this problem 14 years ago when I started working in EDA, but haven’t paid much attention since then.

So, I scoured the congressional… Read More

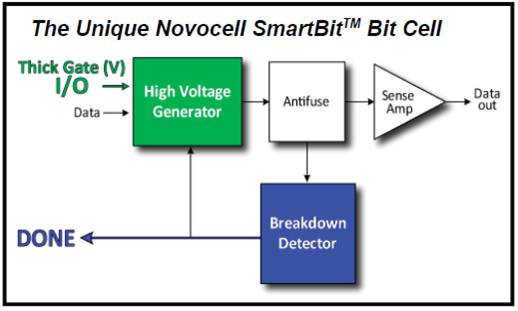

Selecting Non Volatile Memory IP: dynamic programming from Novocell Semiconductor lead to a lower “Cost Of Ownership”

NVM IP offering from NovocellSemiconductor is based on SmartBit, an antifuse, One Time Programmable (OTP) technology, and the OTP block are embedded in standard Logic CMOS without any additional process or post process steps and can be programmed at the wafer level, in package, or in the field, as end user requires. What makes … Read More

Did You Know Venus is Transiting the Sun During DAC 2012?

On Tuesday, June 5th, starting at 3:05 pm in San Francisco, the planet Venus will cross, or transit, the sun. If you stop by Ciranova’s DAC booth #1608 anytime on Monday or Tuesday, they will give you a free pair of solar viewing glasses that will let you view the transit safely.

According to the NASA website, Transits of Venus… Read More

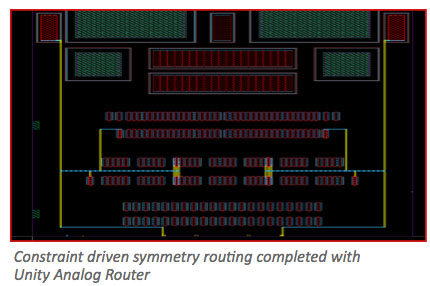

After Planning Comes Implementation for Pulsic

Automation for digital design has been mainstream for a couple of decades but place and route for analog is still in its infancy. Many attempts have been made over the years to automate analog design in one way and another, the bodies are piled up on the hillside. Much analog design is still largely done with custom layout and circuit… Read More

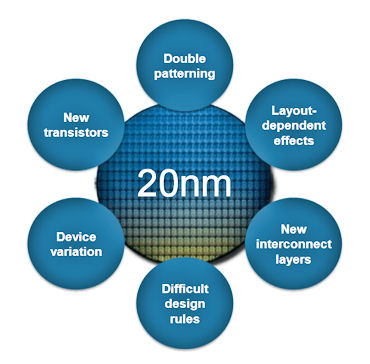

Layout Migration and DRC Correction at DAC 2012

In the world of sub-40nm IC design, as feature size decreases with each new process node, it becomes increasingly difficult to migrate a layout to a new process technology. Too many factors impact manufacturability and yield. At each new process node, to make sure that a given layout is manufacturable and yields well, it is subject… Read More

Novocell Semiconductor Update 2012!

Since most of you have not heard of Novocellthis is more of an introduction but they have been around for 10+ years and are NVM (non-volitile memory) pioneers. NVM has evolved into a critical part of the semiconductor ecosystem which is why I sought them out. While SiDense and Kilopass bury each other in legal fees Novocell is doing… Read More

♫ If you are going to San Francisco, be sure to….

Well, you can wear flowers in your hair if you like, but it is a bit sixties. However, here are some things that I do recommend that you be sure to do.

Some of these recommendations require you to find a given numbered pier. The Ferry Building at the end of Market Street is effectively pier 0. Odd numbers go north (including pier 1½ ). Even… Read More

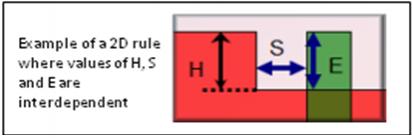

Sagantec Update: More EDA Consolidation!

Adding sophisticated 2D dynamic compaction technology to address 20nm and 14nm challenges. Santa Clara, California – May 3 ,2012 – Sagantec today announced that it has acquired Dutch startup NP-Komplete Technologies BV (Eindhoven, The Netherlands) for its physical design compaction and migration solutions based on a sophisticated… Read More

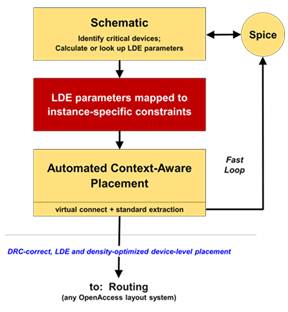

A Simple, Scalable LDE Optimization Flow for 28/20nm Custom/AMS Design

At 28nm and below, a number of electrical variation effects become significant which depend not only on individual devices, but the physical interaction between neighboring devices, wells, etc during the manufacturing process. Some of these effects have become collectively referred to as “Layout Dependent Effects” (LDE);… Read More

Things From Intel 10K That Make You Go …. Hmmmm