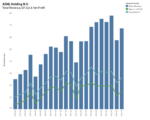

- AMAT reports good but underwhelming quarter

- China slowing creates revenue & GM headwinds- ICAPs weak

- AI remains the one and only bright spot in both foundry & memory

- Cyclical recovery remains slow – Single digit Y/Y growth

OK quarter – still slow growing, revs up only 5% Y/Y

AMAT came in at revenues of $6.78B… Read More

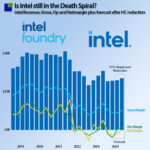

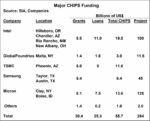

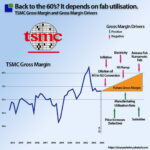

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?