Semidynamics has taken a significant step forward in the race to build next-generation AI infrastructure with the unveiling of its 3nm AI inference silicon and a vertically integrated, full-stack systems strategy. Announced in February 2026, the development marks the company’s evolution from an advanced architecture specialist… Read More

2026 Outlook with Volker Politz of Semidynamics

Tell us a little bit about yourself and your company.

I am the Chief Sales Officer for Semidynamics and I lead the global sales team and drive the overall sales process.

Semidynamics was founded in 2016 as a design service company with a focus on RISC-V. This was so successful that the CEO decided to pivot the company towards its own … Read More

Semidynamics Inferencing Tools: Revolutionizing AI Deployment on Cervell NPU

In the fast-paced world of AI development, bridging the gap from trained models to production-ready applications can feel like an eternity. Enter Semidynamics’ newly launched Inferencing Tools, a game-changing software suite designed to slash deployment times on the company’s Cervell RISC-V Neural Processing… Read More

From All-in-One IP to Cervell™: How Semidynamics Reimagined AI Compute with RISC-V

In an era where artificial intelligence workloads are growing in scale, complexity, and diversity, chipmakers are facing increasing pressure to deliver solutions that are not only fast, but also flexible and programmable. Semidynamics recently announced Cervell™, a fully programmable Neural Processing Unit (NPU) designed… Read More

Vision-Language Models (VLM) – the next big thing in AI?

AI has changed a lot in the last ten years. In 2012, convolutional neural networks (CNNs) were the state of the art for computer vision. Then around 2020 vison transformers (ViTs) redefined machine learning. Now, Vision-Language Models (VLMs) are changing the game again—blending image and text understanding to power everything… Read More

Semidynamics adds NoC partner and ONNX for RISC-V AI applications

When Semidynamics added support for int4 and fp8 data types to their RISC-V processors, it clearly indicated their intent to target AI inference with hundreds or perhaps thousands of concurrent threads running in their advanced caching and pipelining scheme. Two recent announcements around Embedded World 2025 reinforce their… Read More

2025 Outlook with Volker Politz of Semidynamics

Tell us a little bit about yourself and your company.

I am the Chief Sales Officer and I lead the global sales team and drive the overall sales process.

Semidynamics was founded 2016 as a design service company with a focus on RISC-V. This was so successful that the CEO decided to pivot the company towards its own IP sales and started… Read More

Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V Solution

Founded with a vision to create transformative, customizable IP solutions, Semidynamics has emerged as a significant player in the AI hardware industry. Initially operating as a design engineering company, Semidynamics spent its early years exploring various pathways before pivoting to develop proprietary intellectual… Read More

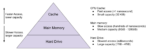

Gazzillion Misses – Making the Memory Wall Irrelevant

Memory Hierarchy and the Memory Wall

Computer programs mainly move data around. In the meantime, they do some computations on the data but the bulk of execution time and energy is spent moving data around. In computer jargon we say that applications tend to be memory bound: this means that memory is the main performance limiting … Read More

CEO Interview: Roger Espasa of Semidynamics

Roger Espasa is the CEO and founder of Semidynamics, an IP supplier of two RISC-V cores, Avispado (in-order) and Atrevido (out-of-order) supporting the RISC-V vector extension and Gazzillion(tm) misses, both targeted at HPC and Artificial Intelligence. Prior to the foundation of the company, Roger was Technical Director/Distinguished… Read More