You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 178

[name] => IP

[slug] => ip

[term_group] => 0

[term_taxonomy_id] => 178

[taxonomy] => category

[description] => Semiconductor Intellectual Property

[parent] => 0

[count] => 1989

[filter] => raw

[cat_ID] => 178

[category_count] => 1989

[category_description] => Semiconductor Intellectual Property

[cat_name] => IP

[category_nicename] => ip

[category_parent] => 0

[is_post] =>

)

by Jagadish Nayak

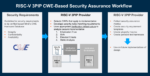

RISC-V adoption continues to accelerate across commercial and government microelectronics programs. Whether open-source or commercially licensed, most RISC-V processor cores are integrated as third-party IP (3PIP), potentially introducing supply chain security challenges that demand structured,… Read More

The rapid evolution of automotive technology has intensified the demand for highly reliable, high-performance semiconductor memory solutions. Modern vehicles increasingly rely ADAS driving features, and complex infotainment platforms, all of which require memory that can operate flawlessly under extreme environmental… Read More

Non-volatile memory choices are becoming more complex as SoC designs push into advanced nodes, and new requirements driven by AI, new sensor technologies and stringent quality standards.

The second annual 2025 NVM Survey, completed in December, captures a market that still hangs on established technologies but is increasingly… Read More

As computing expands from data centers to edge devices, semiconductor designers face increasing pressure to optimize both performance and energy efficiency. Advanced process nodes continue to provide transistor-level improvements, but scaling alone cannot meet the demands of hyperscale AI infrastructure or ultra-low-power… Read More

Akeana Inc. announced a key milestone in the development of its advanced RISC-V technology: a successful partnership with Axiomise Limited to formally verify its super-scalar test chip, Alpine. The collaboration highlights the growing importance of formal verification in ensuring correctness, performance, and efficiency

…

Read More

At the 2025 RISC-V Summit, amid debates over cloud scaling and AI cost, DeepComputing CEO Yuning Liang offered a radical view: the future of intelligence isn’t in the cloud at all — it’s already in your pocket. His lunchtime conversation began with iPhones and ended with the death of the operating system. In between, he sketched … Read More

In the rapidly evolving world of artificial intelligence and semiconductor design, open-standard processor architectures are gaining unprecedented traction. At the center of this shift is SiFive, a company founded by the original creators of the RISC-V ISA, which champions an open, extensible, and license-free alternative… Read More

Artificial intelligence is rapidly moving beyond the digital domain and into the physical world. From autonomous robots and smart factories to intelligent vehicles and connected consumer devices, AI systems are increasingly expected to perceive their surroundings, make real-time decisions, and act on them instantly. This… Read More

Up to now the RISC-V community has been developing open-source processor implementations to a stage where they can appeal to system designers looking for alternatives to proprietary Arm and x86 cores. Toward this end, two projects have emerged as particularly significant examples of where RISC-V is heading. One is Ara, a vector… Read More

For more than a decade, progress in artificial intelligence has been framed almost entirely through the lens of compute. Faster GPUs, denser accelerators, and higher TOPS defined each new generation. But as generative and agentic AI enter their next phase, that framing is no longer sufficient. The most advanced AI systems today… Read More

Beyond Moore’s Law: High NA EUV Lithography Redefines Advanced Chip Manufacturing