In the rapidly evolving world of artificial intelligence hardware, memory bandwidth and data movement have become just as important as raw compute power. Addressing this challenge head-on, Semidynamics has announced a strategic investment aimed at accelerating the development of its next-generation memory-centric AI … Read More

Semiconductor Intellectual Property

The “New Shift-Left”: Why FPGA Prototyping is the Ultimate RISC-V IP Sandbox

In the EDA world, “Shift-Left” has traditionally been a mantra for early software development—booting the OS before the silicon even leaves the fab. But as the RISC-V revolution accelerates, the goalposts have moved. We are seeing the emergence of a “New Shift-Left”, one that focuses on critical architectural… Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI Era

With the launch of its new P570 Gen 3 processor family, SiFive is making a broader statement about the future of edge computing and the growing role of RISC-V in mainstream application processors. Rather than simply unveiling another CPU core, the company is positioning the P570 as a balanced-performance processor built specifically… Read More

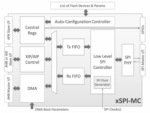

Configurable xSPI memory controller IP core is FuSa-ready

SPI, invented some four decades ago, is so successful as a low-pin-count interface for microcontrollers and processor cores that it spurred memory makers to incorporate both the physical signaling interface and advanced memory command protocols into serial flash and serial pseudo-SRAM (PSRAM) devices. Those protocols, … Read More

CEO Interview with Dave Kelf, CEO of Breker Verification Systems

In the functional verification space, Breker Verification Systems stands out for its vast and long-standing understanding and ability to solve many of the seemingly intractable complexity challenges, especially in the system space.

I recently talked with Dave Kelf, Breker’s CEO, who has plenty of good news to share about Breker’s… Read More

Synopsys and TSMC Deepen AI Design Alliance: What It Means

A recent announcement from Synopsys signals a meaningful escalation in the race to build next-generation AI hardware. The expanded collaboration between Synopsys and TSMC brings together silicon-proven IP, AI-driven design tools, and cutting-edge manufacturing processes in a tightly integrated effort to accelerate high-performance… Read More

Connecting the Dots: Why RISC-V System Design Is Entering a New Era

At the recent RISC-V Now event hosted by Andes, the discussion underscored the fact that RISC-V is no longer just about instruction set architecture advantages or customizable cores. The real focus has moved up the stack to system-level design. This is where connectivity, integration, and security define whether an innovation… Read More

Advanced Microelectronics Paving the Way for 6G with Alphacore

The world stands at the threshold of a new era in wireless communication as research communities, standards bodies, and technology companies begin shaping what will become sixth generation mobile networks. While fifth generation systems are still expanding across global markets, attention has already shifted toward defining… Read More

WAVE-N Specialized Video Processing NPU for Edge AI Systems

The rapid growth of AI applications in edge devices has created a strong demand for specialized hardware capable of performing high-performance neural network inference under strict power and latency constraints. Traditional CPUs and GPUs often struggle to meet the efficiency requirements of embedded and mobile systems.… Read More

Scalable Network-on-Chip Enables a Modular Chiplet Platform

The semiconductor industry is undergoing a profound transformation as system complexity, performance expectations, and time-to-market pressures continue to rise. Traditional monolithic system-on-chip (SoC) designs are increasingly giving way to modular, chiplet-based architectures that enable flexibility, scalability,… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior