Register management tools have been used mostly in a bottom-up approach. There are some documents and/or spreadsheets created by the System Architects that are delivered to the design and verification teams. They then start capturing the HW/SW interface of the peripheral IPs in their in-house or commercial register management… Read More

Achieving 400W Thermal Envelope for AI Datacenter SoCs

Successful ASIC providers offer top-notch infrastructure and methodologies that can accommodate varied demands from a multitude of customers. Such ASIC providers also need access to best-in-class IP portfolio, advanced packaging and test capabilities, and heterogeneous chiplet integration capability among other things.… Read More

INNOVA PDM, a New Era for Planning and Tracking Chip Design Resources is Born

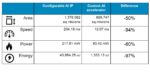

No doubt that the design success of nowadays system on chips (SoCs) is directly linked to the success of cost control. More market opportunities are open for less expensive system on chips and electronic systems.

Both the design cost prediction and the resource tracking during the design process, are key to such a success

Predicting… Read More

IDEAS Online Technical Conference Features Intel, Qualcomm, Nvidia, IBM, Samsung, and More Discussing Chip Design Experiences

Ansys is hosting IDEAS Digital Forum 2022, a no-cost virtual event that brings together industry executives and technical design experts to discuss the latest in EDA for Semiconductors, Electronics, and Photonics.

See the full online conference agenda and list of speakers at www.ansys.com/IDEAS. The free registration will… Read More

TSMC OIP – Enabling System Innovation

On November 10th I watched the presentation by L.C. Lu, TSMC Fellow & VP, as he talked about enabling system innovation with dozens of slides in just 26 minutes. TSMC is the number one semiconductor foundry in the world, and their Open Innovation Platform (OIP) events are popular and well attended as the process technology and… Read More

2023: Welcome to the Danger Zone

I just got this notice from my good friend and fellow sailor Rich Curtin. The Silicon Catalyst events are the best open networking events in Silicon Valley, absolutely. And this one includes another good friend Wally Rhines, the most interesting man in semiconductors, so you don’t want to miss this. The live event will definitely… Read More

Pushing Acceleration to the Edge

As more AI applications turn to edge computing to reduce latencies, the need for more computational performance at the edge continues to increase. However, commodity compute engines don’t have enough compute power or are too power-hungry to meet the needs of edge systems. Thus, when designing AI accelerators for the edge, Joe… Read More

TSMC Expands the OIP Ecosystem!

This was the 12th TSMC OIP and it did not disappoint. The attendance was back to pre pandemic levels, there was interesting news and great presentations. We will cover the presentations in more depth after the virtual event which is on November 10th. You can register HERE.

As I mentioned in my previous post, the Jim Keller Keynote … Read More

TSMC 2022 Open Innovation Platform Ecosystem Forum Preview

One of my favorite events is just around the corner and that is the TSMC OIP Ecosystem Forum and it’s at my favorite Silicon Valley venue the Santa Clara Convention Center. Nobody knows more about the inner workings of the ecosystem than TSMC so this is the premier semiconductor collaboration event, absolutely.

In my 40 years as a … Read More

Measuring Success in Semiconductor Design Optimization: What Metrics Matter?

When it comes to electronic design automation (EDA), there are two aspects to this technologically challenging and highly competitive field. First, there is the task of designing very complex chips for which a full suite of various software tools are needed. Then there is the task of managing extremely complex EDA workflows and… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center