Many know Arteris as the “network-on-chip”, or NoC, company. Through acquisitions and forward-looking development, the footprint for Arteris has grown beyond smart interconnect IP. At DAC this year, Arteris highlighted its latest expansion with a new SoC integration automation product called Magillem Packaging. The announcement… Read More

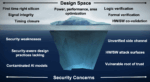

Caspia Focuses Security Requirements at DAC

As expected, security was a big topic at DAC this year. The growth of AI has demanded complex, purpose-built semiconductors to run ever-increasing workloads. AI has helped to design those complex chips more efficiently and with less power demands. There was a lot of discussion on these topics. But there is another part of this trend.… Read More

WEBINAR: Edge AI Optimization: How to Design Future-Proof Architectures for Next-Gen Intelligent Devices

Edge AI is rapidly transforming how intelligent solutions are designed, from smart home devices to autonomous vehicles, healthcare gadgets, and industrial IoT. Yet, architects, chip designers, and product managers frequently grapple with a common and daunting challenge: creating efficient, high-performance AI solutions… Read More

WEBINAR Unpacking System Performance: Supercharge Your Systems with Lossless Compression IPs

In today’s data-driven systems—from cloud storage and AI accelerators to automotive logging and edge computing—every byte counts. The exponential growth in data volumes, real-time processing demands, and constrained bandwidth has made efficient, lossless data compression a mission-critical requirement. Software-based… Read More

ChipAgents Tackles Debug. This is Important

Innovation is never ending in verification, for performance, coverage, connection to verification plans and other aspects of DV. But debug, accounting for 40% of the verification cycle, has remained stubbornly resistant to significant automation. Debug IDEs help to visualize but don’t address the core problem: given a failure,… Read More

Webinar – Power is the New Performance: Scaling Power & Performance for Next Generation SoCs

What if you could reduce power and extend chip lifetime, without compromising performance? We all know the importance of power optimization for advanced SoCs. Thanks to the massive build out of AI workloads, power consumption has gone from a cost or cooling headache to an existential threat to the planet, if current power consumptions… Read More

DAC News – A New Era of Electronic Design Begins with Siemens EDA AI

AI is the centerpiece of DAC this year. How to design chips to bring AI algorithms to life, how to prevent AI from hacking those chips, and of course how to use AI to design AI chips. In this latter category, there were many presentations, product announcements and demonstrations. I was impressed by many of them. But an important observation… Read More

Arteris at the 2025 Design Automation Conference #62DAC

Key Takeaways:

- Expanded Multi-Die Solution: Arteris showcases its foundational technology for rapid chiplet-based innovation. Check out the multi-die highlights video.

- Ecosystem compatibility: Supported through integration with products from major EDA and foundry partners, including Cadence, Synopsys, and global

Secure-IC at the 2025 Design Automation Conference #62DAC

Secure-IC at DAC 2025: Building Trust into Tomorrow’s Chips and Systems

As semiconductor innovation accelerates, the chiplet-based design paradigm is redefining the landscape of advanced electronic systems. At DAC 2025, Secure-IC (booth #1208) will present a comprehensive suite of technologies engineered to address the… Read More

Podcast EP293: 3DIC Progress and What’s Coming at DAC with Dr. John Ferguson and Kevin Rinebold of Siemens EDA

Dan is joined by Dr. John Ferguson, Director of Product Management for the Calibre nmDRC and 3DIC related products for Siemens EDA. John has worked extensively in the area of physical design verification. Holding several patents, he is also a frequent author in the physical design and verification domain. Current activities … Read More

Memory Matters: Signals from the 2025 NVM Survey