I’ve spent many years in the ASIC business, and I’ve seen my share of complex chip tapeouts. All of these projects share one important challenge – compute requirements explode when you get close to the finish line. Certain tools need to run on the full-chip layout for final verification and the run times for those tools can get excessively… Read More

Radiation Tolerance. Not Just for ISO 26262

Years before ISO 26262 (the auto safety standard) existed, a few electronics engineers had to worry about radiation hardening, but not for cars. Their concerns were the same we have today – radiation-induced single event effects (SEE) and single event upsets (SEU). SEEs are root-cause effects – some form of radiation, might be… Read More

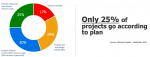

PSS, Test Realization and Reuse

Mentor just released a white paper on this topic which I confess has taxed my abilities to blog the topic. It’s not that the white paper is not worthy – I’m sure it is. I’m less sure that I’m worthy to blog on such a detailed technical paper. But I’m always up for a challenge, so let’s see what I can make of this, extracting a quick and not very… Read More

Mentor Masterclass on ML SoC Design

I was scheduled to attend the Mentor tutorial at DVCon this year. Then coronavirus hit, two big sponsors dropped out and the schedule was shortened to three days. Mentor’s tutorial had to be moved to Wednesday and, as luck would have it, I already had commitments on that day. Mentor kindly sent me the slides and audio from the meeting… Read More

5G SoCs Demand New Verification Approaches

Lately, I’ve been cataloging the number of impossible-to-verify technologies we face. All forms of machine learning and inference applications fall into this category. I’ve yet to see a regression test to prove a chip for an autonomous driving system will do the right thing in all cases. Training data bias is another interesting… Read More

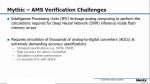

Mentor Helps Mythic Implement Analog Approach to AI

The entire field of Artificial Intelligence (AI) has resulted from what is called “first principles thinking”, where problems are re-examined using a complete reassessment of the underlying issues and potential solutions. It is a testament to how effective this can be that AI is being used for a rapidly expanding number of applications… Read More

High-Level Synthesis at the Edge

Custom AI acceleration continues to gather steam. In the cloud, Alibaba has launched its own custom accelerator, following Amazon and Google. Facebook is in the game too and Microsoft has a significant stake in Graphcore. Intel/Mobileye have a strong lock on edge AI in cars and wireless infrastructure builders are adding AI capabilities… Read More

Mentor at DVCON 2020!

Are you ready for the premier conference for functional design and verification of electronic systems?

Sponsored by Accellera Systems Initiative, DVCon is an independent, not-for-profit organization dedicated to creating design and verification standards required by systems, semiconductor, intellectual property (IP)… Read More

It’s The Small Stuff That Gets You …

The last session I attended at DesignCon 2020 wasn’t a session at all. Rather it was an interactive discussion with Todd Westerhoff, product manager for electronic board systems at Mentor Graphics. Todd made some observations about the way high-performance PCBs are designed today and perhaps the way they should be designed. … Read More

Bringing Hierarchy to DFT

Hierarchy is nearly universally used in the SoC design process to help manage complexity. Dealing with flat logical or physical designs proved unworkable decades ago. However, there were a few places in the flow where flat tools continued to be used. Mentor lead the pack in the years around 1999 in helping the industry move from … Read More