You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4440

[filter] => raw

[cat_ID] => 157

[category_count] => 4440

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Last Monday I met with Nobuto Ono, VP Business development at Jedat (Japan EDA Technologies) while attending the DAC conference.

The company started in Tokyo and is Ex Seiko Instruments, in 2004.

Main product – layout editor for IC (SX 9000). New system is ALpha SX in 2002. 2007 listed on JASDAQ market. Like Virtuoso tools,… Read More

Atrenta presented an update on the TSMC Soft IP Alliance Program at TSMC’s theater each day at DAC. Mike Gianfagna, Atrenta VP of Marketing, presented an introduction to SpyGlass, an overview of the program and a progress report. Dan Kochpatcharin, TSMC Deputy Director of IP Portfolio, was also there. Between Mike, Dan, and I there… Read More

Just up the road from Cambridge-based ARM in Kings Langley is Imagination Technologies, their biggest competitor in the GPU market. Interestingly they also were a customer of VLSI Technology in the early days back when they were called Videologic. Tomorrow, jointly with Carbon, they are announcing that a wide range of their PowerVR,… Read More

So DAC is over and you are no longer thinking about the features and benefits of new tools or even the tools that you already own. But once you have lots of tools then you need to worry about how to use them efficiently.

But here are three things that you need to worry about to get the most out of your EDA investment:

- how do you measure the actual

…

Read More

Kathryn Kranen, CEO of Jasper was elected chairman of EDAC for 2012-2014. She has has 20 years EDA industry. She started her career as a design engineer at Rockwell International and then joined Daisy Systems (one of the DMV, the second generation of EDA companies). She then moved to be VP of North American sales at Quickturn (emulation)… Read More

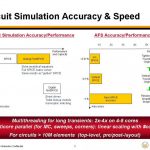

I caught the Berkeley Design Automation presentation in the TSMC Theater, where Simon Young (BDA’s director of product marketing) described the Analog FastSPICE (AFS) nanometer circuit verification platform, built on their foundation of very fast, very accurate, high capacity circuit simulation.

BDA claims the AFS platform… Read More

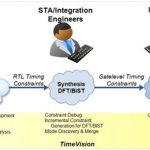

Ausdia’s Timevisionby Paul McLellan on 06-11-2012 at 8:05 pmCategories: EDA

I met Sam Appleton of Ausdia during DAC. I found it quite hard to understand exactly what they do. I’ve talked before about something that I nick-named City Slickers’ Marketing. It is named after the following exchange from the movie City Slickers:Curly: Do you know what the secret of life is? [holds up one finger] This.… Read More

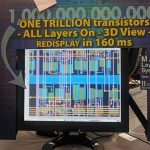

There are only a handful of billion transistor IC designs in existence today, so when an EDA company touts 1 trillion transistor IC layout editing then I take notice. This year at DAC I met with Katherine Hayes and Karen Mangum of Micro Magic to get an update on their IC layout tools.… Read More

I first heard about SPICE Vision Pro when working at Mentor Graphics where we needed a way to visualize SPICE netlists and debug SPICE simulation results node by node on a design where we didn’t have the original schematics. Last Monday I met the engineers from Concept Engineering in their booth at DAC to get an update, Gerhard… Read More

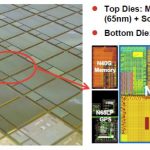

Cadence/TSMC 3Dby Paul McLellan on 06-11-2012 at 5:16 pmCategories: Cadence, EDA

Mark Twain remarked that everyone talks about the weather but nobody does anything about it. 3D ICs seems to be a bit like that. Over the last couple of years there have been lots of people talking about 3D but very little that has actually been manufactured. In addition to the weather, everyone talks about Xilinx’s 3D Virtex… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era