You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4439

[filter] => raw

[cat_ID] => 157

[category_count] => 4439

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

Did you watch Atrenta’s holiday video (it’s only one minute)? Various Atrenta employees from all over the world wished you happy holidays in their own languages. Now Atrenta are having a competition. If you identify all the languages in the video then you can win an iPad Mini.

To enter the competition, or to view the … Read More

Our world is decidedly analog, made up of stimuli for our five basic senses of sight, touch, hearing, taste, and smell, and more advanced senses like balance and acceleration. To be effective on the Internet of Things, digital devices must integrate with the analog world, interfacing with sensors and control elements.… Read More

It has been a year since my article Semiconductor Landscape in Jan 2012 I wanted to look back into the major events over the year and then anticipate what’s in store going forward. What has happened over the year is much more than what I could foresee. Major consolidation in EDA space – Synopsys acquired Magma, SpringSoft, Ciranova,… Read More

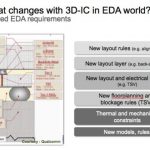

A couple of weeks ago was the 3D Architectures for Semiconductor Integration and Packagingconference in Redwood City. Cadence presented the changes that they have been making to their tool flow to enabled 2.5D (interposer-based) and true 3D TSV-based designs. You know what TSV stands for by now right? Through-silicon-via, … Read More

I have no idea if chicken was actually on the menu, but on December 12, Calibre RealTime picked up its thirdindustry award, this time the 2012 Elektra Award for Design Tools and Development Software from the European Electronics Industry. Calibre RealTime came out on top in a group full of prestigious finalists, including ByteSnap,… Read More

Anyone who has been around technology consortia or standards bodies will tell you that the timeline from inception to mainstream adoption of a new embedded technology is about 5 years, give or take a couple dream cycles. You can always tell the early stage, where very different concepts try to latch on to the same, simple term.

Such… Read More

There are two primary microprocessor companies in the world these days: Intel and ARM. Of course there are many others but Intel is dominant on the PC desktop (including Macs) and ARM is dominant in mobile (including tablets).

One of the keynotes at last month’s Jasper User Group (JUG, not the greatest of acronyms) was by Bob… Read More

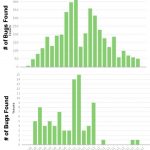

Design For Manufacturing (DFM) is the art and science of making an IC design yield better in order to receive a higher ROI. Ian Smith, an AE from Mentor in the Calibre group presented a pertinent webinar, IP Scoring Using TSMC DFM Kits. I’ll provide an overview of what I learned at this webinar.… Read More

We know by now that clock speeds aren’t everything when it comes to measuring the goodness of a processor. Performance has direct ties to pipeline and interconnect details, power factors into considerations of usability, and the unspoken terms of yield drive cost.

My curiosity kicked in when I looked at the recent press release… Read More

Analog, mixed-signal, RF, and custom digital circuitry implemented in GHz nanometer CMOS introduce a new class of design and verification challenges that traditional transistor‑level simulators cannot adequately address. Berkeley Design Automation, Inc., (BDA) was founded in 2003 by Amit Mehrotra and Amit Narayan,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center