Generative AI is dramatically changing the compute power that must be delivered by advanced designs. This demand has risen by more than 10,000 times in the past five to six years. This increased demand has impacted the entire SoC design flow. We are now faced with going beyond 1 trillion transistors per chip, and systems now consist… Read More

Electronic Design Automation

Big Picture PSS and Perspec Deployment

I met Moshik Rubin (Sr. Group Director, Product Marketing and BizDev in the System Verification Group at Cadence) at DVCon to talk about PSS (the Portable Stimulus Standard) and Perspec, Cadence’s platform to support PSS. This was the big picture view I was hoping for, following more down in the details views from earlier talks.… Read More

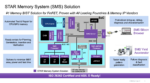

Evolution of Memory Test and Repair: From Silicon Design to AI-Driven Architectures

Memory testing in the early days of computing was a relatively straightforward process. Designers relied on simple, deterministic approaches to verify the functionality of memory modules. However, as memory density increased and systems became more complex, the likelihood of faults also rose. With advancements in memory… Read More

An Important Advance in Analog Verification

Innovation in analog design moves slowly, not from lack of desire for better methods from designers or lack of effort and ideas from design tech innovators, but simply because the space is so challenging. Continuous time and signals, and variances in ambient/process characteristics represent a multi-dimensional space across… Read More

CEO Interview with Dr Greg Law of Undo

Greg Law is a C++ debugging expert, well-known conference speaker, and the founder of Undo. Greg has over 20 years’ experience in the software industry working for the pioneering British computer firm Acorn, as well as NexWave and Solarflare.

Determined to build a tool to ease the pain of debugging complex software, he started… Read More

Upcoming Webinar: Accelerating Semiconductor Design with Generative AI and High-Level Abstraction

We have been hearing so much lately about the power of AI and the potential of technologies like agentic AI to address the productivity gap and complexities of semiconductor designs of today and tomorrow. Currently, however, the semiconductor industry has been slow to adopt generative and agentic AI for RTL design code. There… Read More

Metamorphic Test in AMS. Innovation in Verification

We have talked about metamorphic testing before. Here is a clever application to testing an AMS subsystem. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford, EE292A) and I continue our series on research ideas. As always, feedback welcome.… Read More

Webinar: RF board design flow examples for co-simulating active circuits

In part one of this webinar series, Keysight and Modelithics looked at the use of 3D passive vendor component models supporting highly accurate, automated 3D EM-circuit co-simulation of high-frequency RF board designs. Part two continues the exploration of RF board design flows for simulating active circuits on boards, again… Read More

Going Beyond DRC Clean with Calibre DE

For advanced semiconductor designs, achieving both design rule check clean layouts and optimal electrical performance is crucial for minimizing design iterations, reducing time-to-market and ensuring product reliability. Balancing electrical performance and layout integrity is a difficult task. Achieving an optimal… Read More

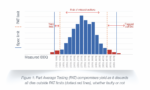

Cut Defects, Not Yield: Outlier Detection with ML Precision

How much perfectly good silicon is being discarded in the quest for reliability? During high-volume chip manufacturing, aggressive testing with strict thresholds may ensure quality but reduces yield, discarding marginal chips that could function flawlessly. On the other hand, prioritizing yield risks allowing defective… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center