IC design challenges are different at advanced nodes like 7nm, so to learn more about the topic I attended a panel luncheon at DAC sponsored by Cadence. The moderator was both funny and technically astute, quite the rare combination, so kudos to Professor Rob Rutenbar, a former Neolinear guy now at the University of Illinois. Panelists… Read More

Electronic Design Automation

AMD’s 7th Generation APU Brings Many Performance Tweaks And The Last Hurrah Before Zen

Advanced Micro Devices has already told us that 2016 was going to be the year of graphics, but the reality is that they also have a lot going on in their CPU and APU division as well. In fact, in addition to Advanced Micro Devices’s newly announced 7th Generation APUs in 2016, the company is also expected to launch their new Zen CPU cores… Read More

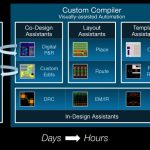

Custom IC Layout Design at #53DAC

Last week at the #53DAC conference there was a lot of excitement in the air about custom IC design, especially at the luncheon that I attended on Tuesday from Synopsys where they had customers like STMicroelectronics, GSI Technology, Samsung Foundry and the Synopsys IP group talk about their experiences using the new Custom Compiler… Read More

Design for the System Age

Of late, it has become painfully obvious that the value of electronics is in the system. And since systems demand continuing improvement, increasing performance and decreasing cost (once partially guaranteed by semiconductor process advances) is now sought through algorithm advances – witness the Google TPU and custom… Read More

The Business of the Semiconductor Business, Part One: What Happened?

This is the first of an occasional series of articles on the semiconductor industry. Many column inches have covered industry consolidation and in this first article, I aim to explain how the industry reached this point. Later articles will cover subjects including China, joint ventures, emerging players like Brazil and Vietnam,… Read More

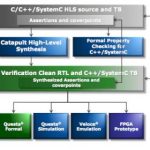

Climbing the Infinite Verification Mountain

Many years ago I read a great little book by Rudy Rucker called “Infinity and the Mind”. This book attempts to explain the many classes of mathematical infinity (cardinals) to non-specialists. As he gets to the more abstract levels of infinity, the author has to resort to an analogy to give a feel for extendible and other cardinal … Read More

Top Ten #53DAC Highlights

Here is a very subjective list of the Top 10 logistical and technical highlights from DAC’53.

(10) With DAC attendance down from its peak days, the Austin Convention Center served as an excellent venue. There was good participation from companies with design centers in the “Silicon Hills”. And, I saw colleagues from Silicon Valley,… Read More

The Evolution of Emulation

Mentor hosted a panel on emulation in their booth at DAC this year. One thing I really liked about this panel is that it didn’t include anyone from Mentor. Not that I have anything against Mentor employees, who are a fine bunch of people from those I know, but I find panels most interesting when the discussion is purely among customers.… Read More

New NVIDIA Tesla M10 Could Drive Enterprise VDI Reassessment

NVIDIA is well known for its leadership in graphics processors (GPUs) for gaming, but their business is quickly diversifying with significant growth in other areas like their datacenter and automotive businesses. Within the datacenter, NVIDIA has been evangelizing a vision for a number of years about the benefits of GPUs for… Read More

AMD Brings More Console Features To PC Gaming

Advanced Micro Devices made a big press splash when they won all three major game console platforms. Their presence inside the Microsoft Xbox One, Sony PS4 and Nintendo Wii U has benefited the company financially at the operating income level and has governed how they design their future GPUs. As Advanced Micro Devices has remained… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center